Discover more than 126 seal ring in vlsi super hot

Update images of seal ring in vlsi by website dienmayquynhon.com.vn compilation. Bridges to Technology: Interfaces, Design Rules, and Libraries | SpringerLink. PPT – ECE 224a Process and Design Rules PowerPoint Presentation, free download – ID:3878530. Investigation on seal-ring rules for IC product reliability in 0.25-μm CMOS technology

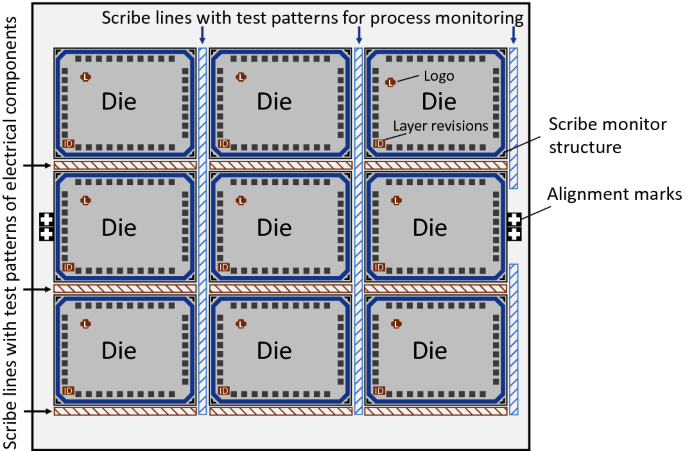

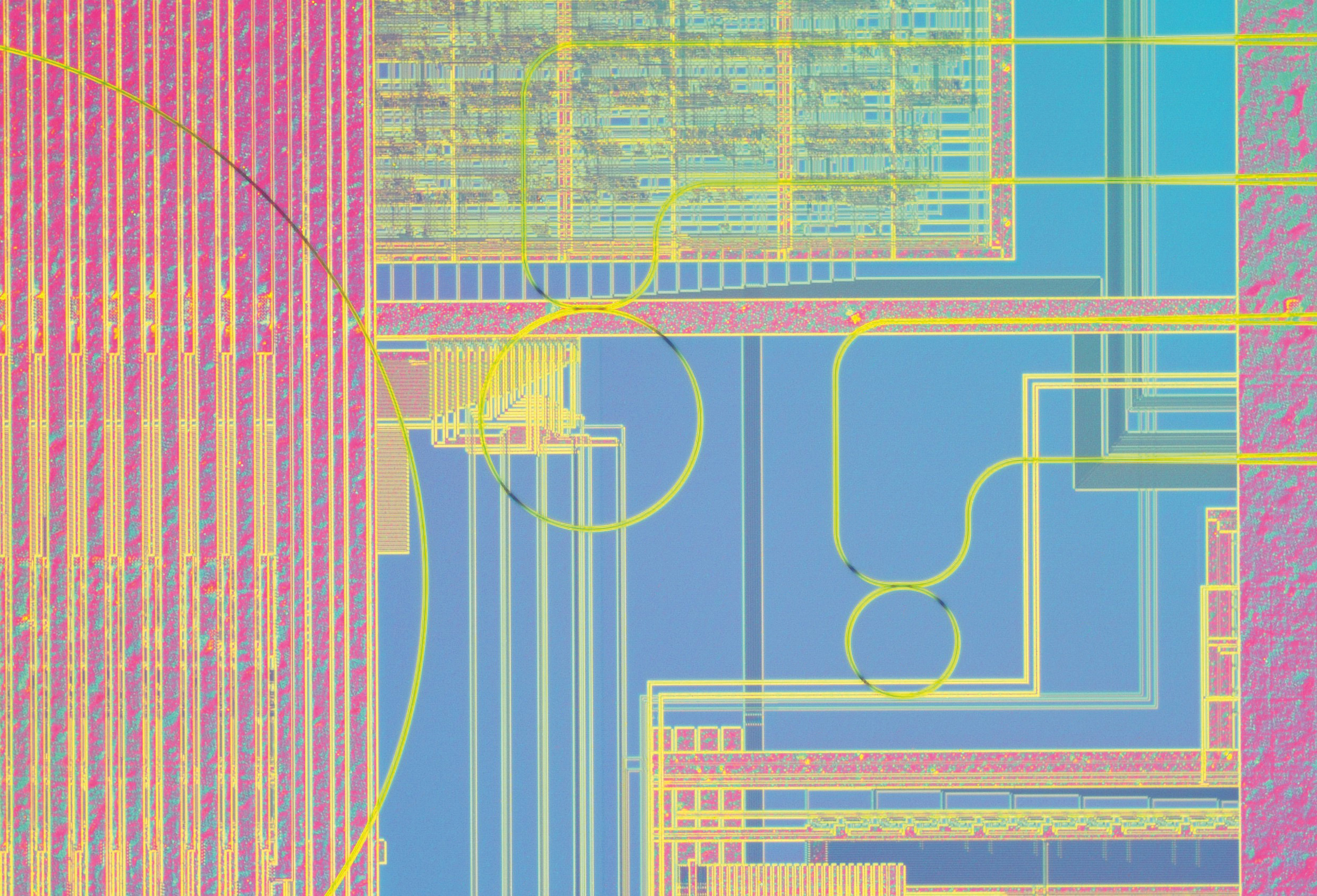

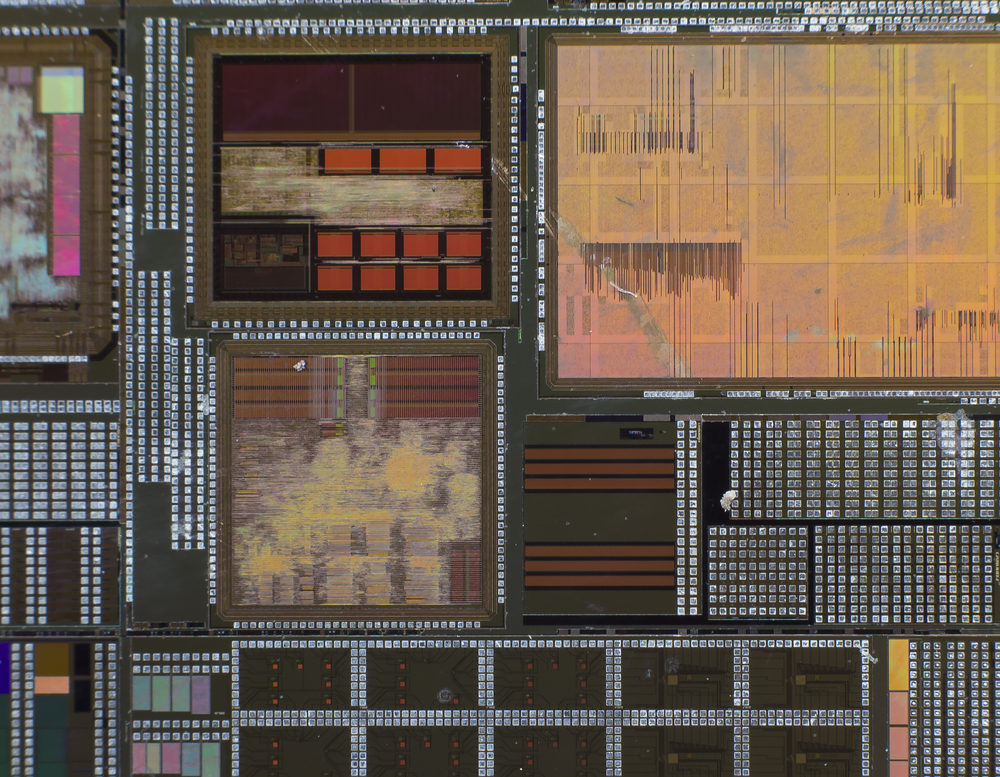

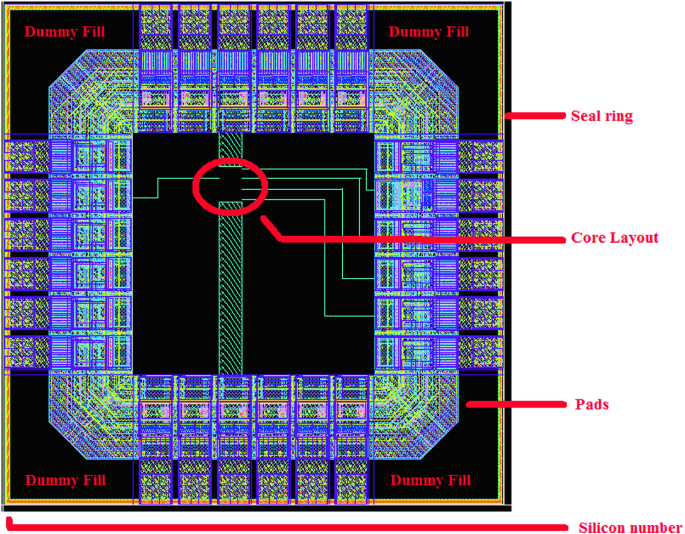

Layout of the analog ASIC. | Download Scientific Diagram – #1

Layout of the analog ASIC. | Download Scientific Diagram – #1

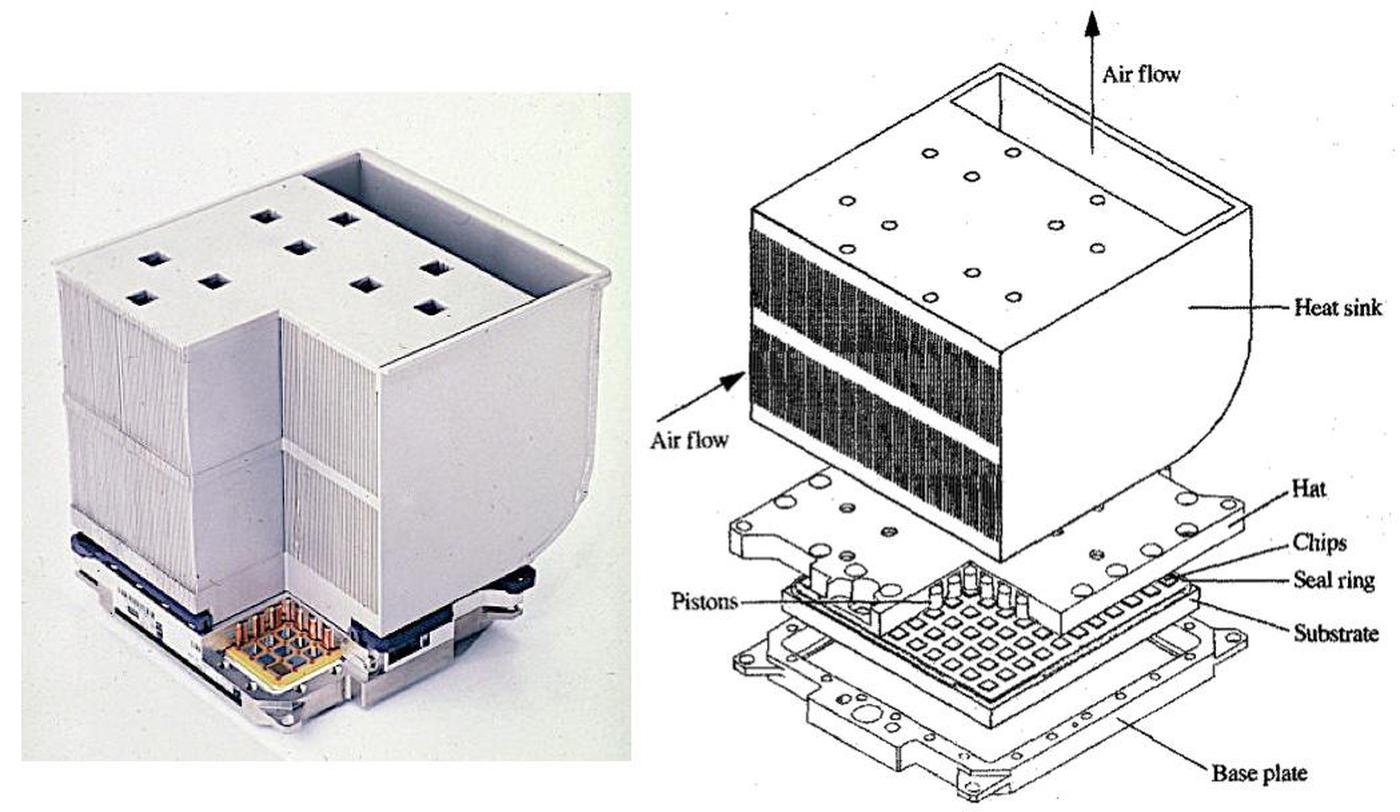

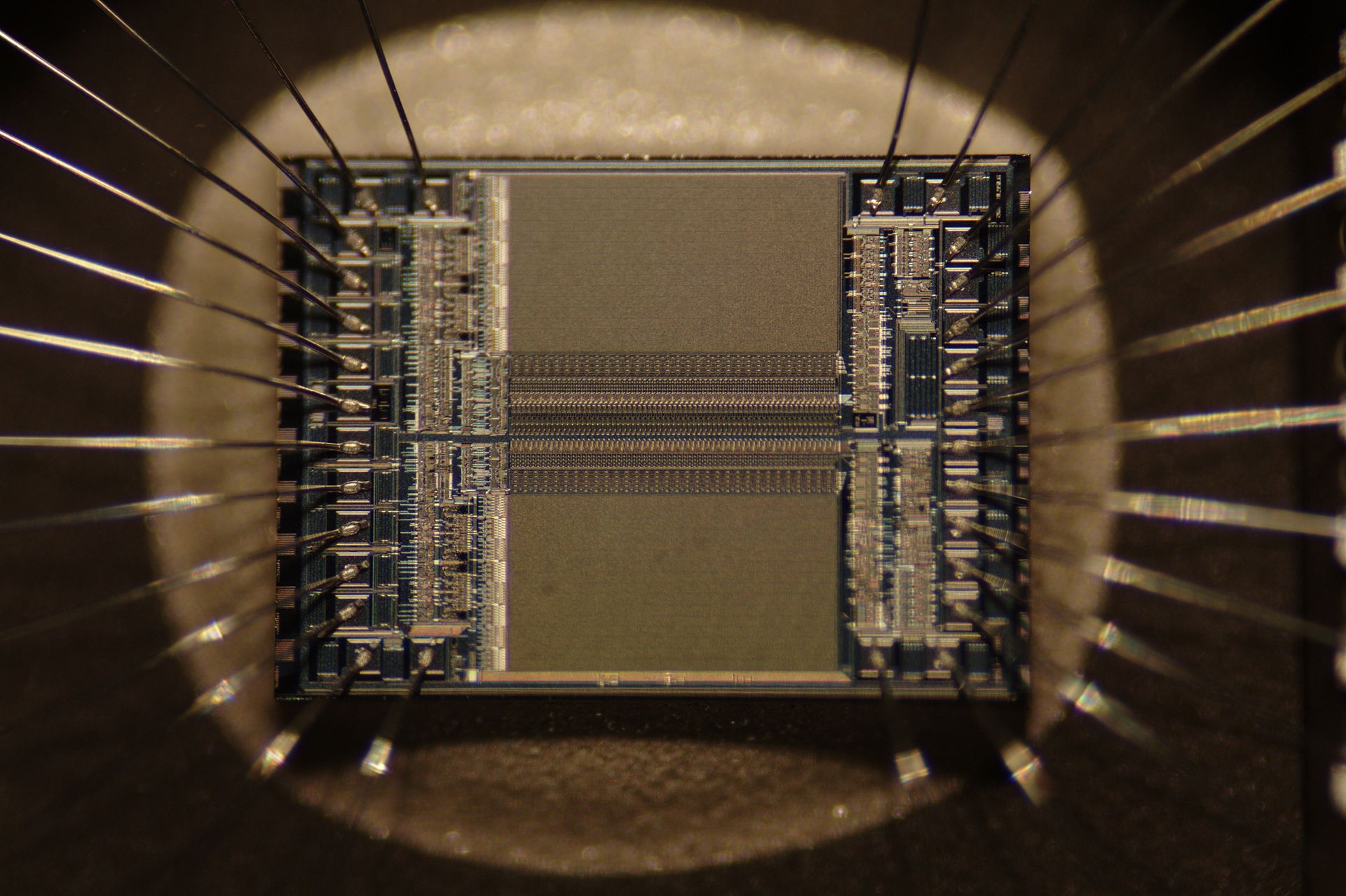

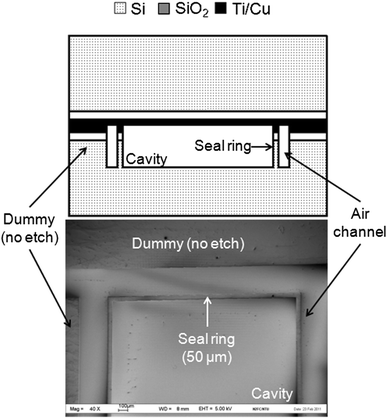

Effect of bonding temperature on hermetic seal and mechanical support of wafer-level Cu-to-Cu thermo-compression bonding for 3D integration | Microsystem Technologies – #2

Effect of bonding temperature on hermetic seal and mechanical support of wafer-level Cu-to-Cu thermo-compression bonding for 3D integration | Microsystem Technologies – #2

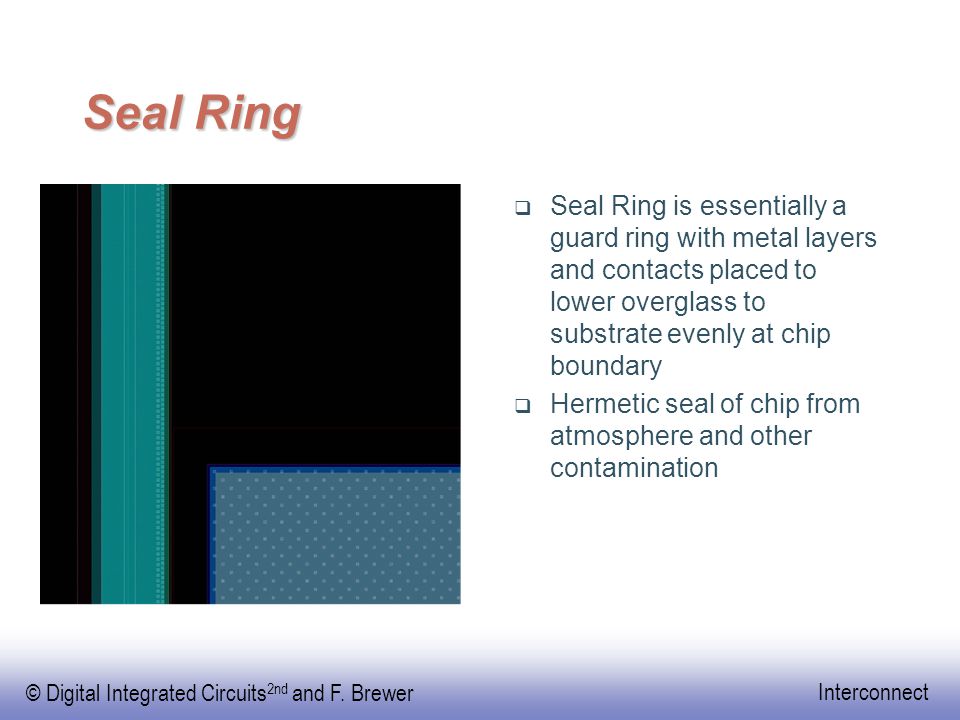

A 0.48 mW High Performance 4-Bit Flash ADC for System-on-Chip Applications in 90 nm CMOS Technology | SpringerLink – #3

A 0.48 mW High Performance 4-Bit Flash ADC for System-on-Chip Applications in 90 nm CMOS Technology | SpringerLink – #3

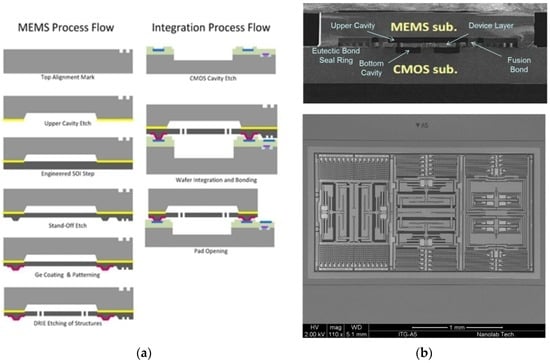

A review of silicon-based wafer bonding processes, an approach to realize the monolithic integration of Si-CMOS and III–V-on-Si wafers – #4

A review of silicon-based wafer bonding processes, an approach to realize the monolithic integration of Si-CMOS and III–V-on-Si wafers – #4

Encyclopedia of Packaging Materials, Processes, and Mechanics : Cu–Cu Direct Bonding – #5

Encyclopedia of Packaging Materials, Processes, and Mechanics : Cu–Cu Direct Bonding – #5

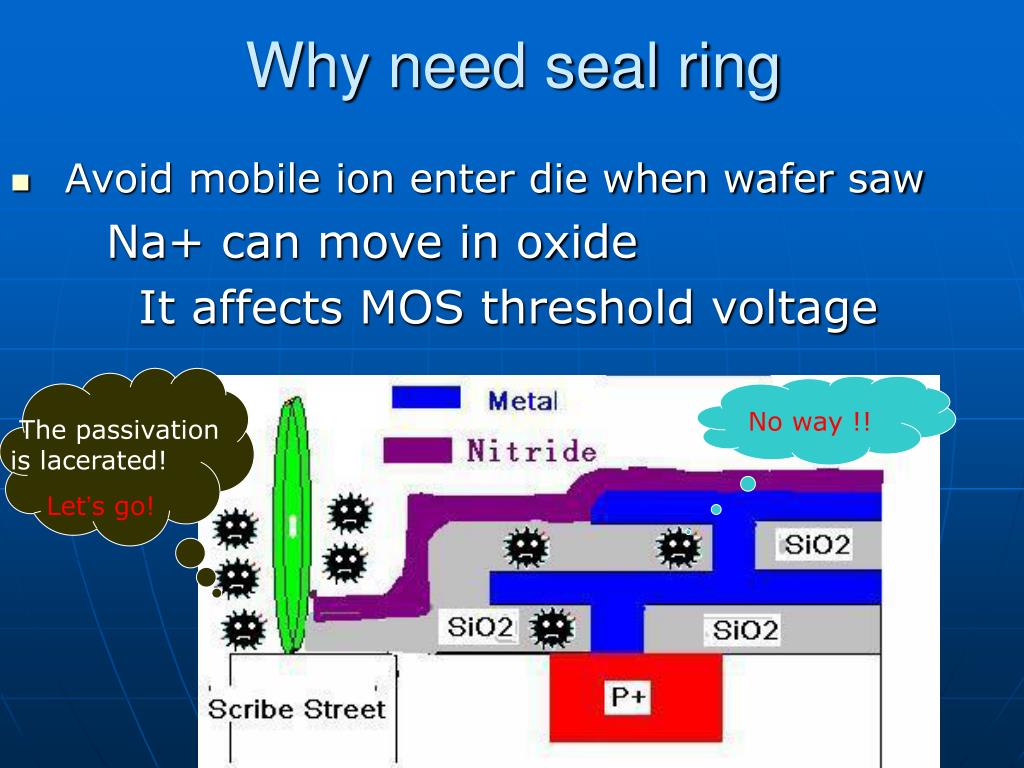

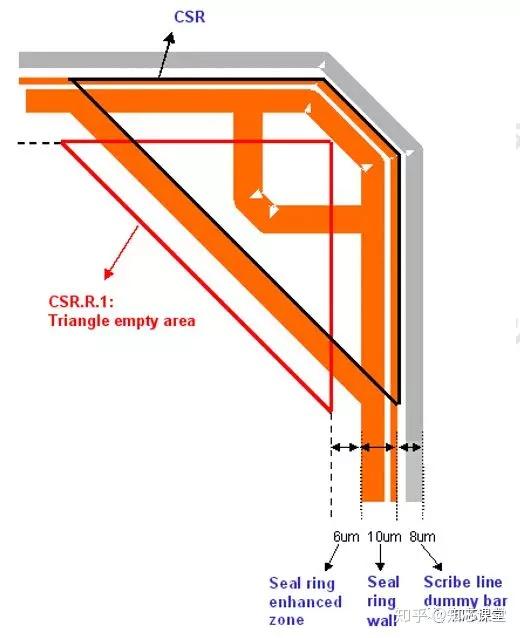

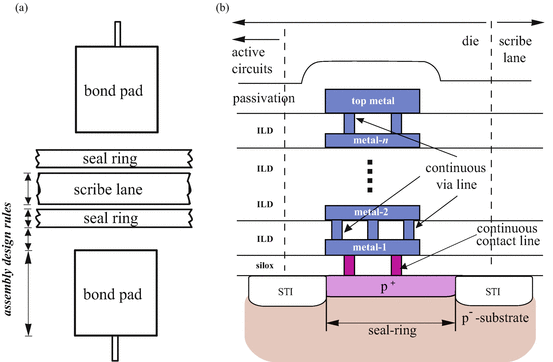

保护神——Seal ring – 知乎 – #6

保护神——Seal ring – 知乎 – #6

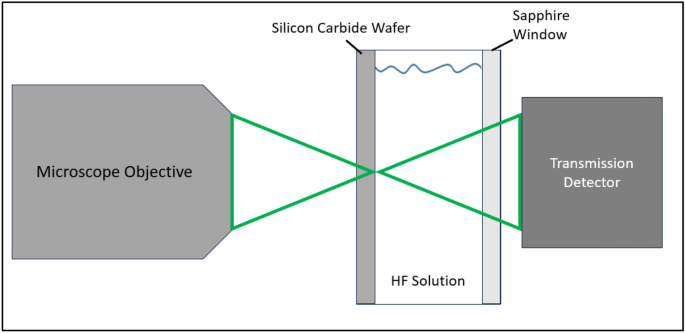

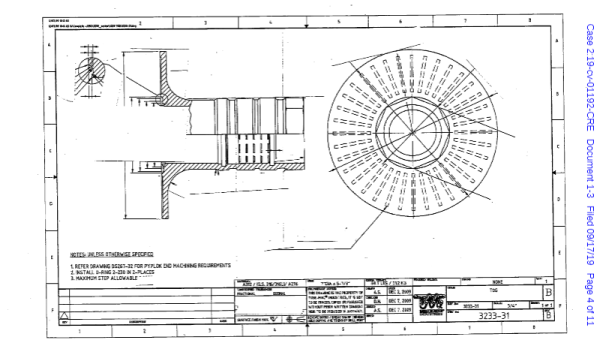

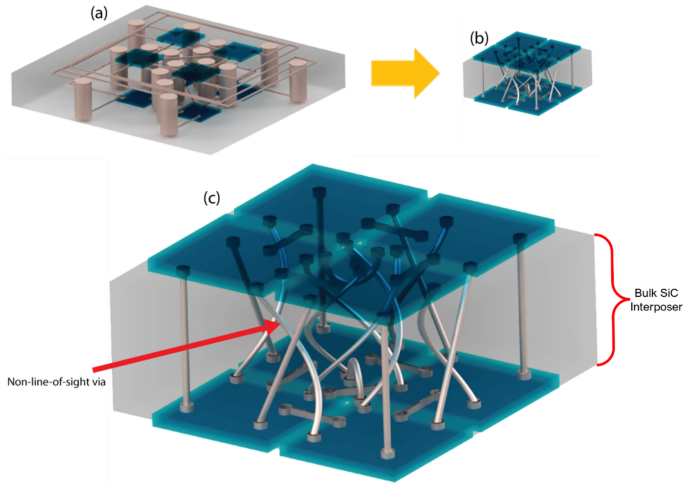

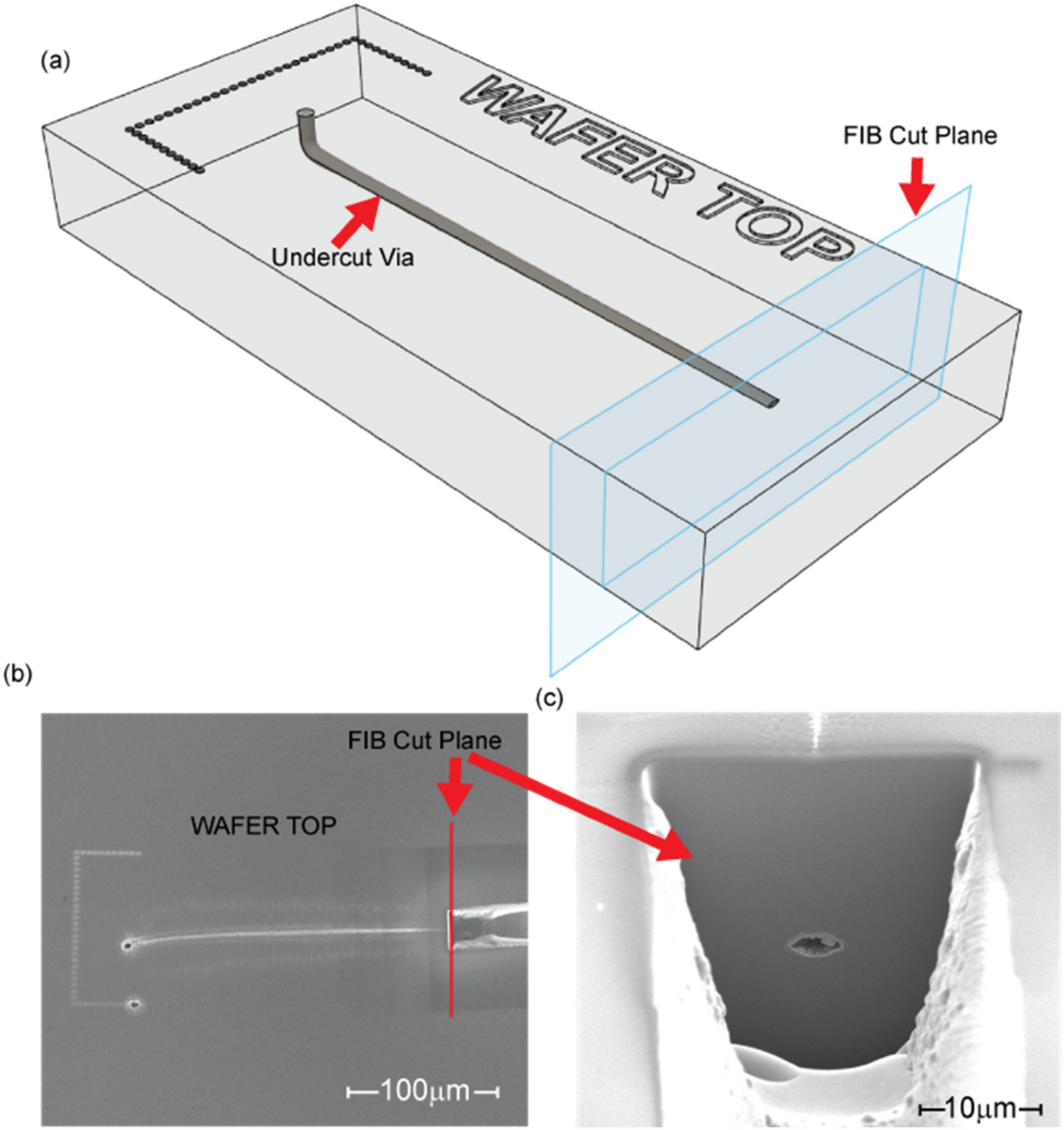

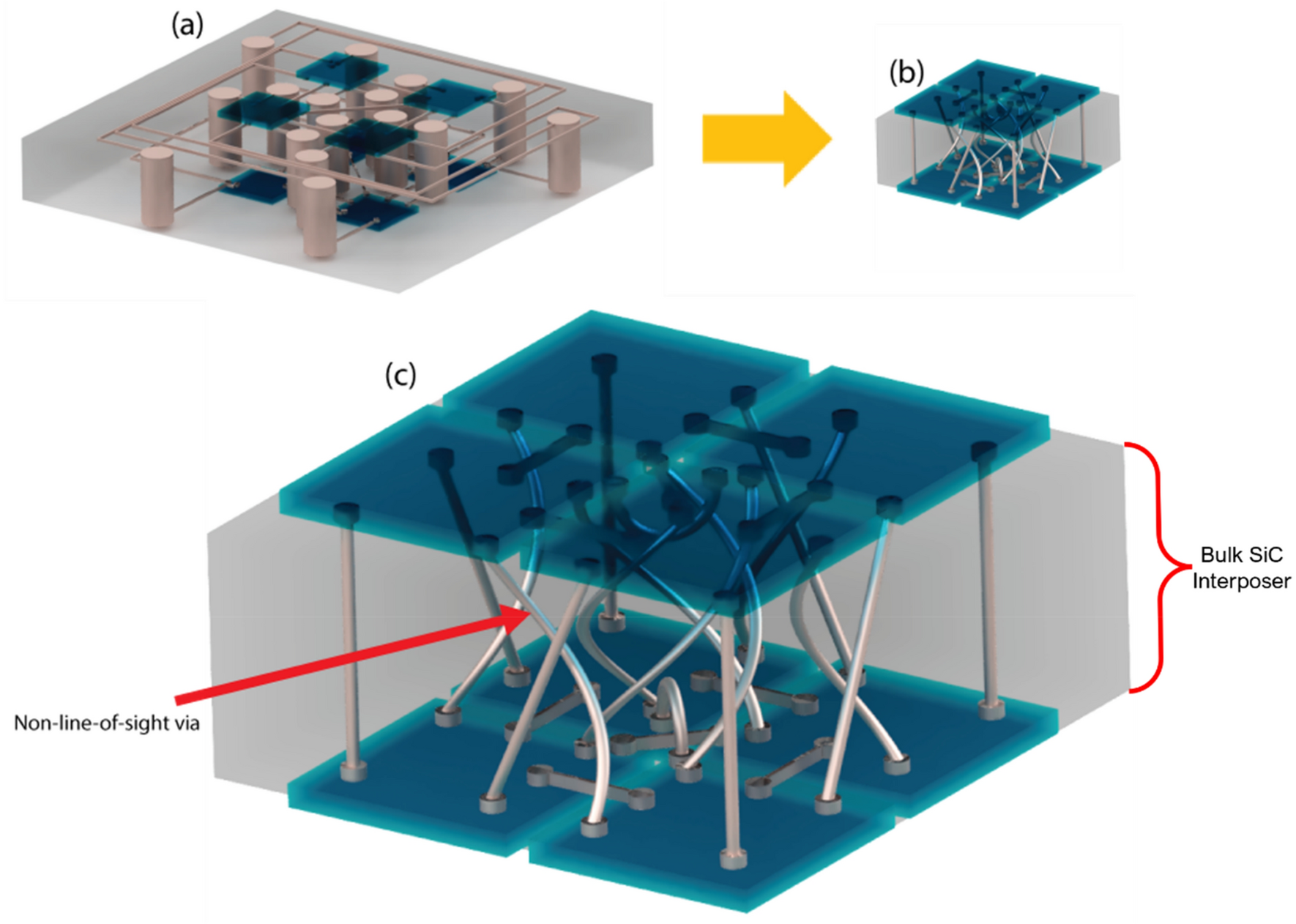

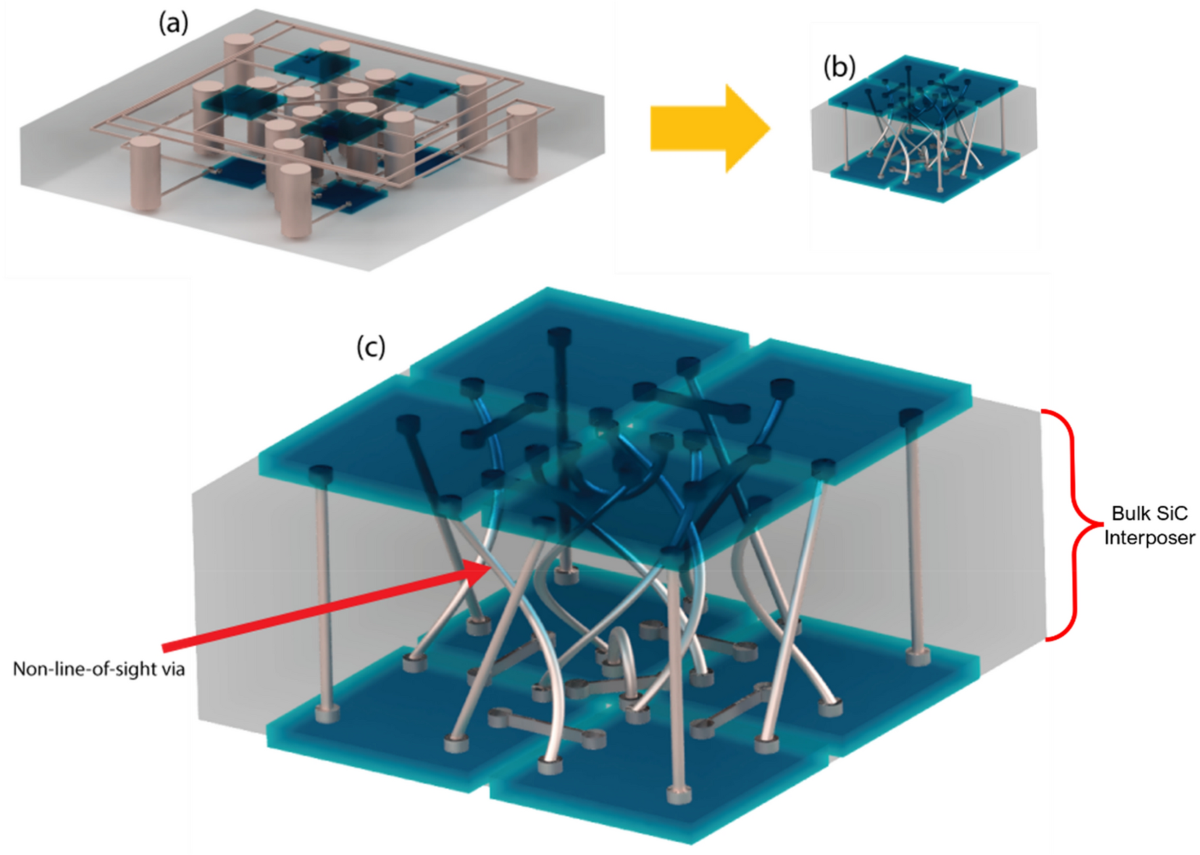

Fabrication of high aspect ratio, non-line-of-sight vias in silicon carbide by a two-photon absorption method | Scientific Reports – #7

Fabrication of high aspect ratio, non-line-of-sight vias in silicon carbide by a two-photon absorption method | Scientific Reports – #7

Unofficial VW 4×3 PowerPoint Template – #8

Unofficial VW 4×3 PowerPoint Template – #8

Bridges to Technology: Interfaces, Design Rules, and Libraries | SpringerLink – #9

Bridges to Technology: Interfaces, Design Rules, and Libraries | SpringerLink – #9

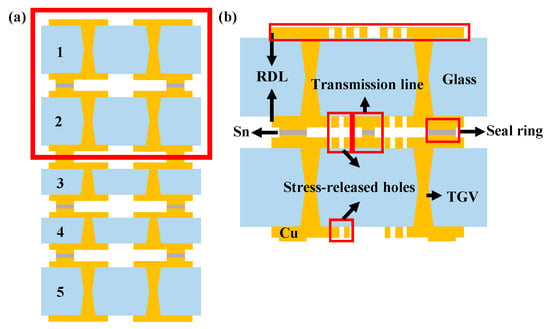

Structures of seal ring based on Cu thermo-compression bonding: (a) 3D… | Download Scientific Diagram – #10

Structures of seal ring based on Cu thermo-compression bonding: (a) 3D… | Download Scientific Diagram – #10

Low Temperature Wafer-Level Metal Thermo-Compression Bonding Technology for 3D Integration | IntechOpen – #11

Low Temperature Wafer-Level Metal Thermo-Compression Bonding Technology for 3D Integration | IntechOpen – #11

- wafer seal ring

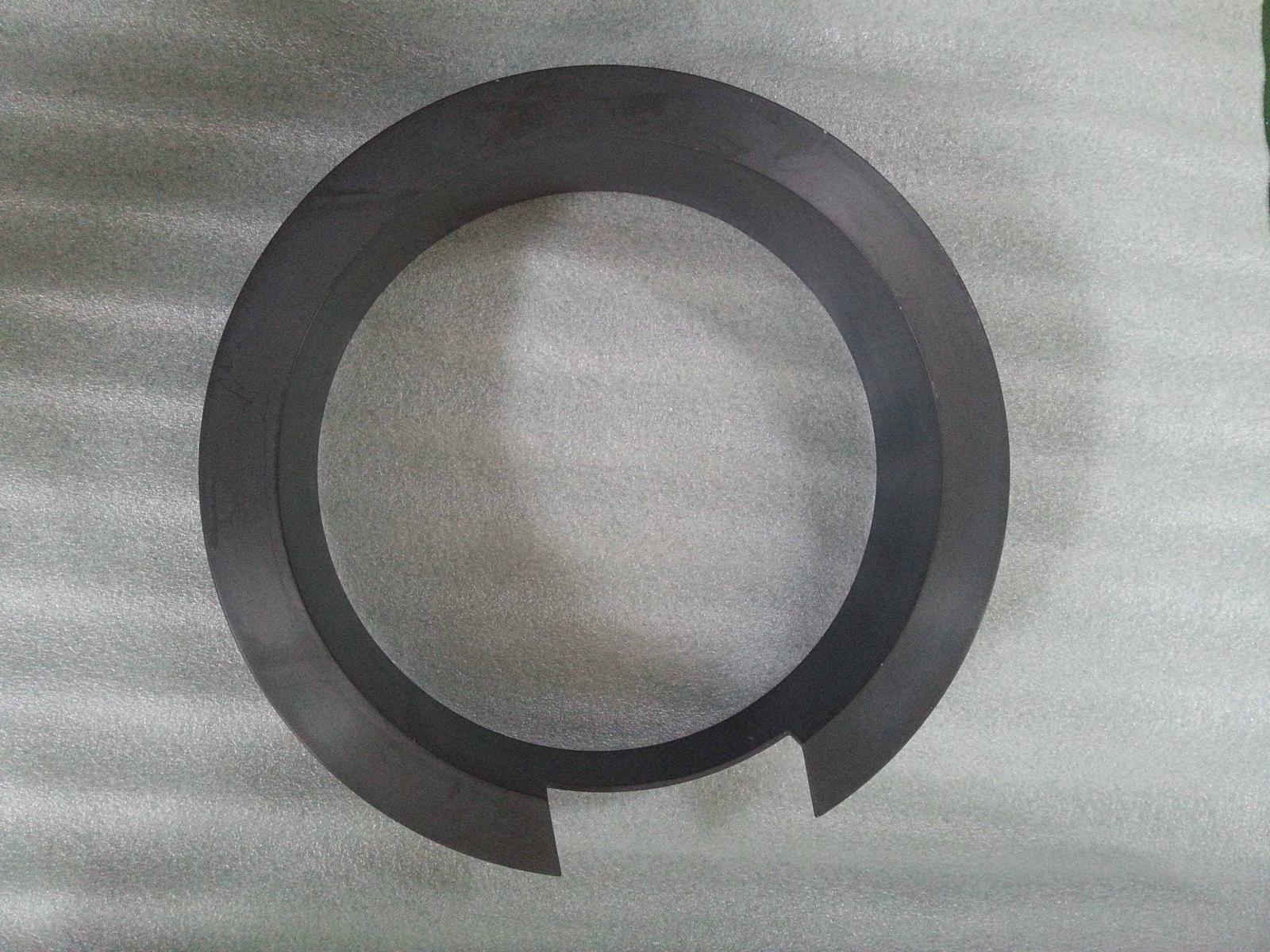

- die seal ring

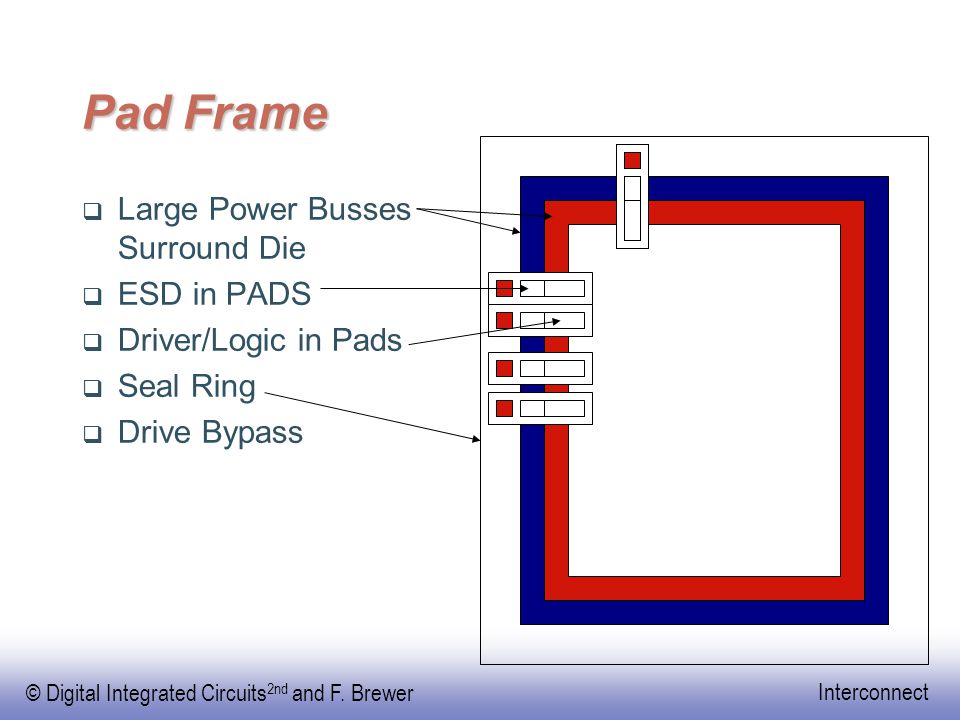

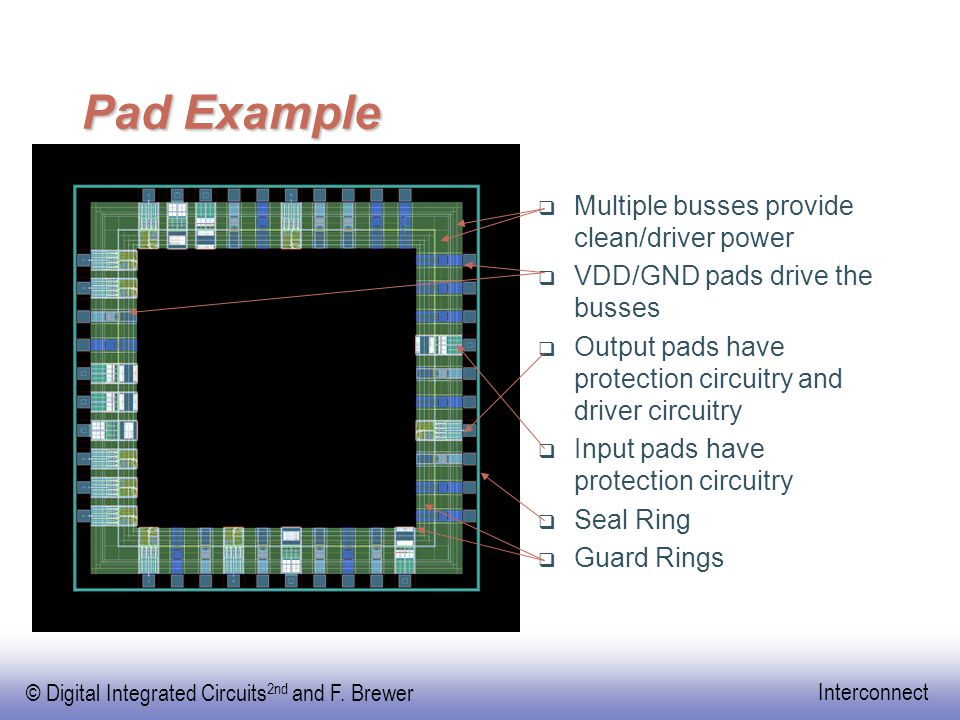

- io pads in vlsi

El E 482 – CMOS/VLSI – Lecture 22 – YouTube – #12

El E 482 – CMOS/VLSI – Lecture 22 – YouTube – #12

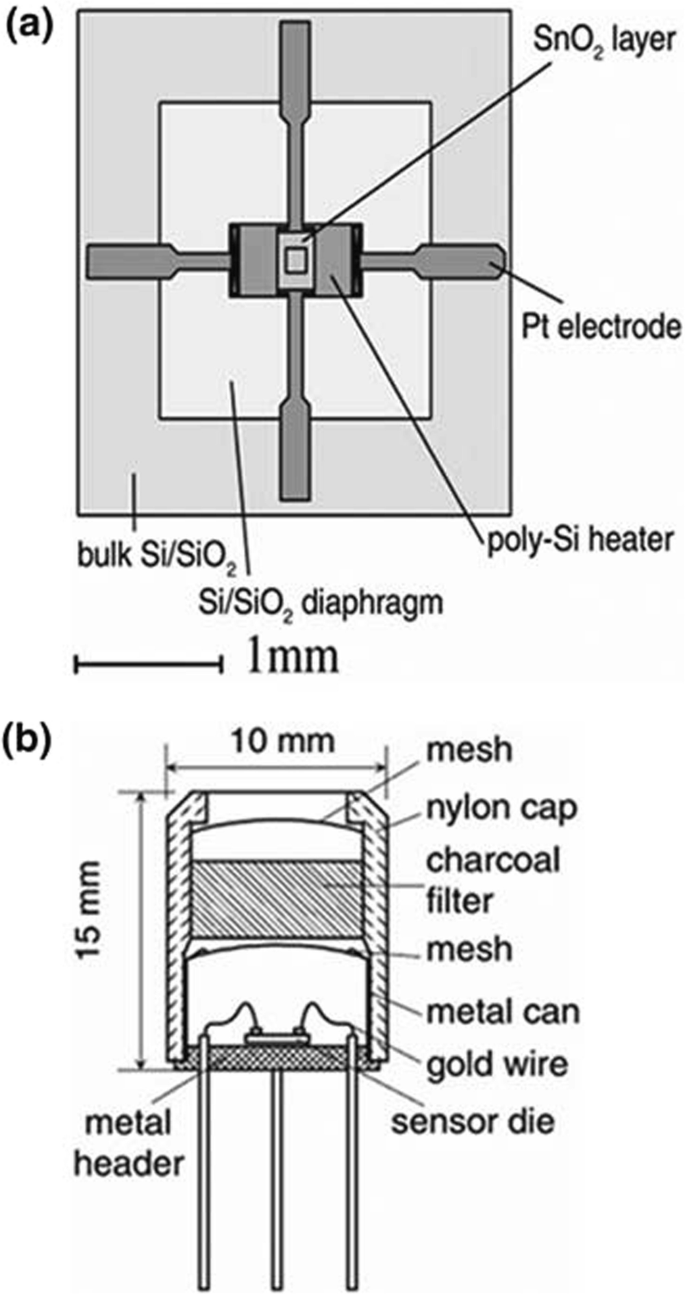

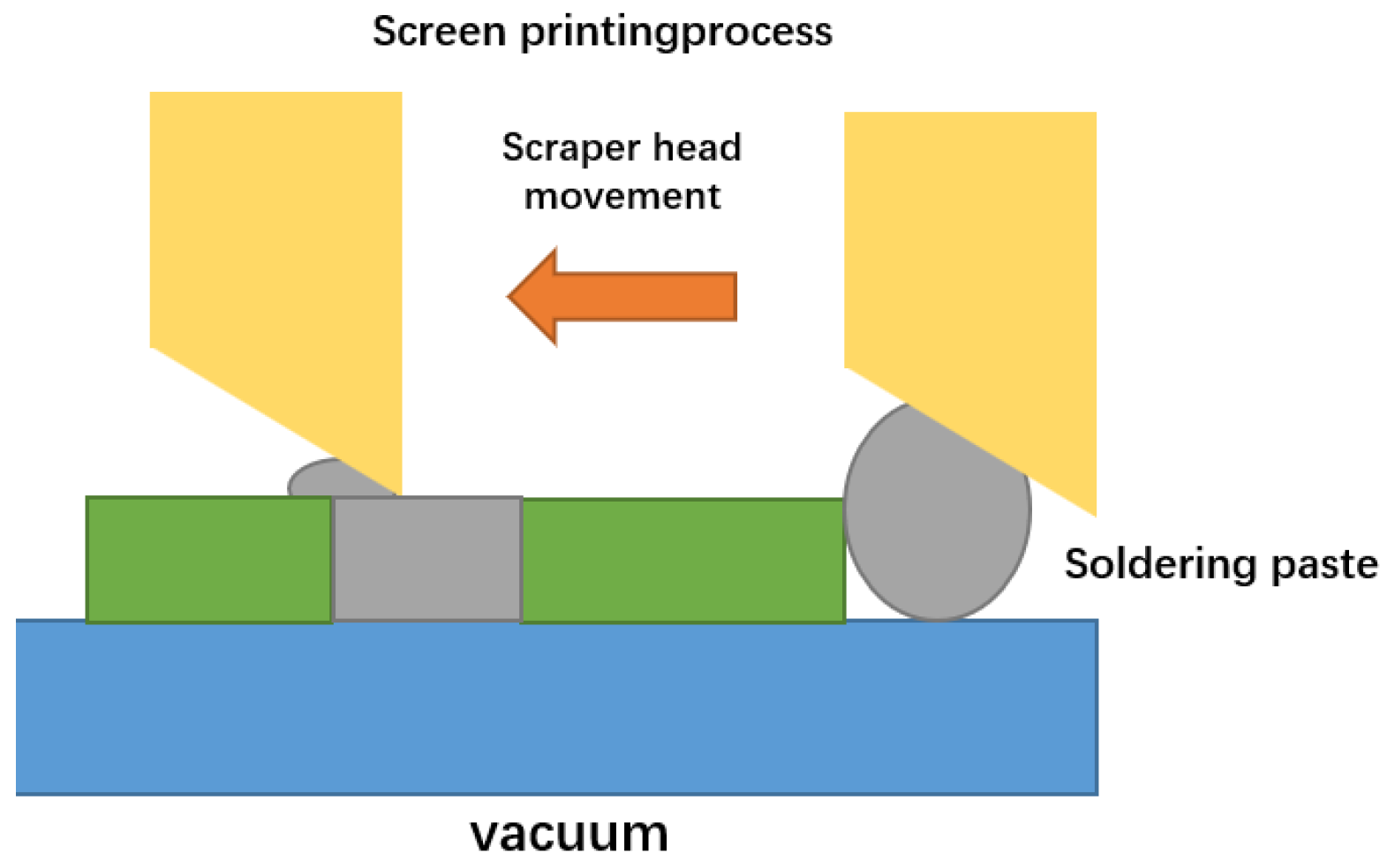

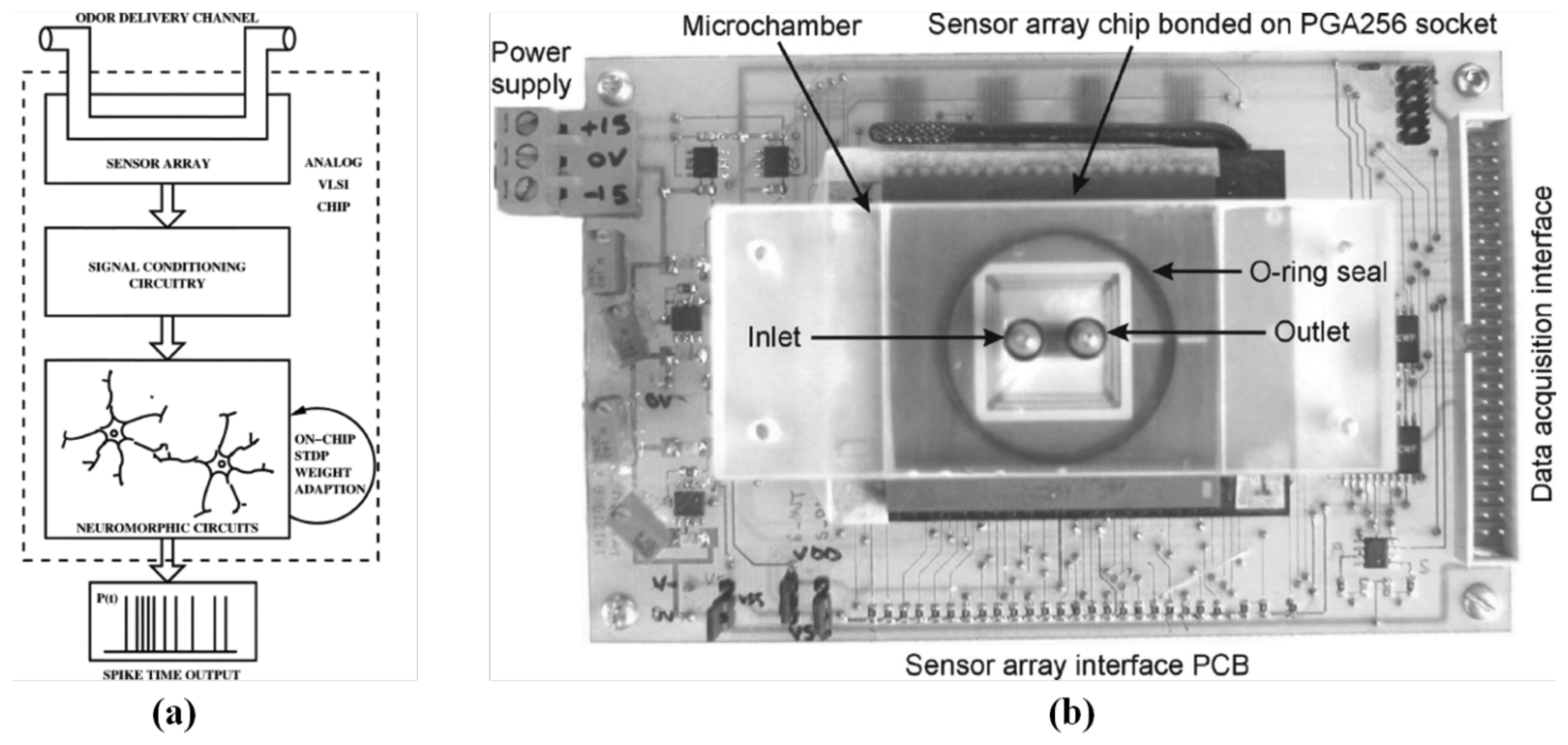

![PDF] Towards a Chemiresistive Sensor-Integrated Electronic Nose: A Review | Semantic Scholar PDF] Towards a Chemiresistive Sensor-Integrated Electronic Nose: A Review | Semantic Scholar](https://slideplayer.com/slide/16986256/98/images/47/S.Bibin+Sam+Paul%2C+IEEE+Student+Branch+NIT-T.jpg) PDF] Towards a Chemiresistive Sensor-Integrated Electronic Nose: A Review | Semantic Scholar – #13

PDF] Towards a Chemiresistive Sensor-Integrated Electronic Nose: A Review | Semantic Scholar – #13

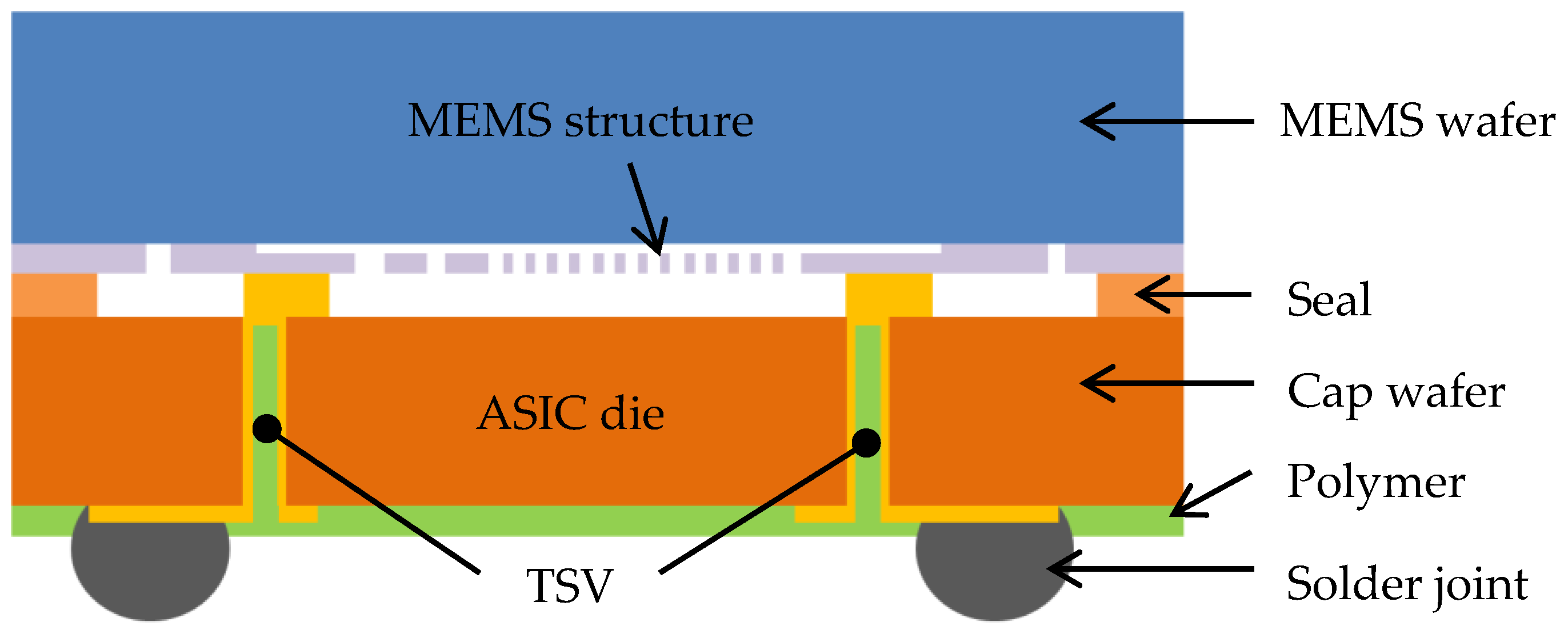

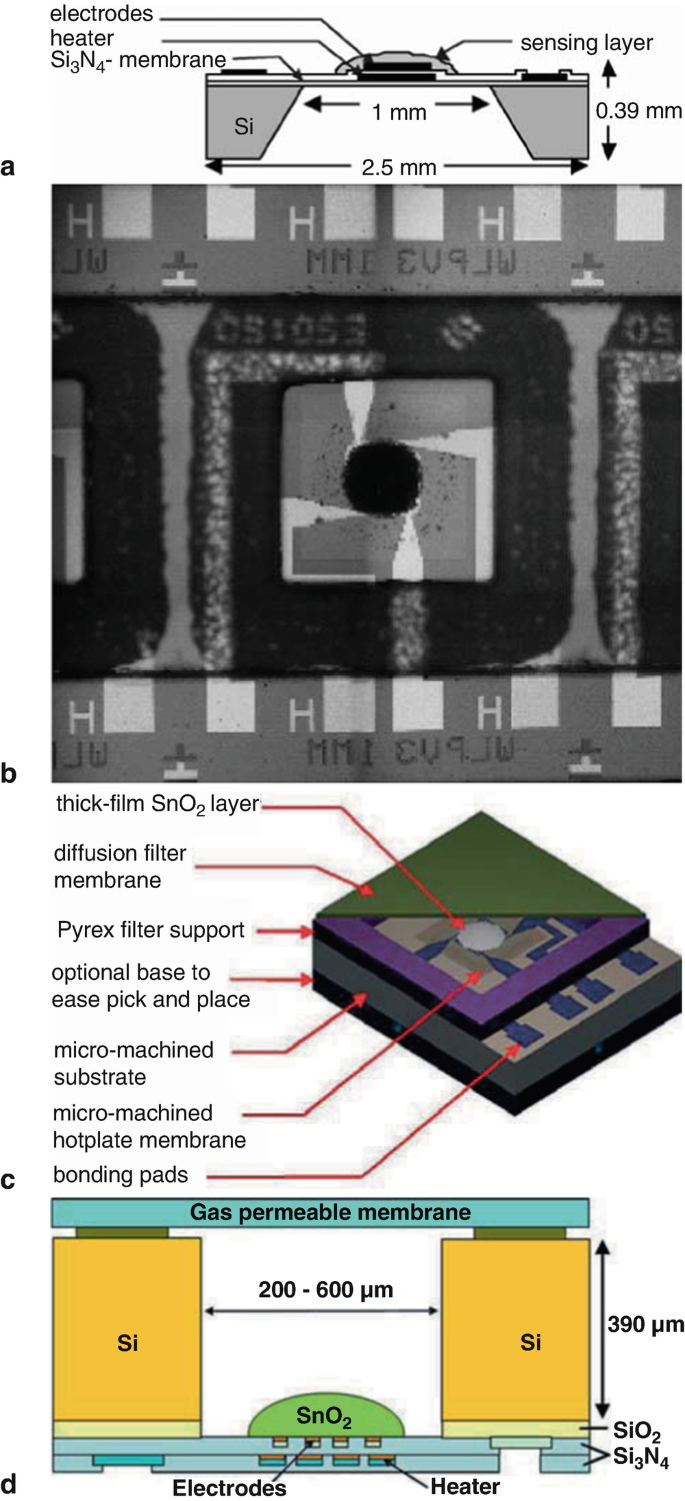

Packaging of Biomolecular and Chemical Microsensors | SpringerLink – #14

Packaging of Biomolecular and Chemical Microsensors | SpringerLink – #14

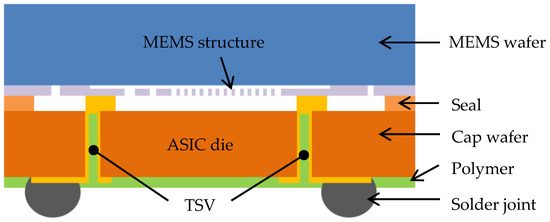

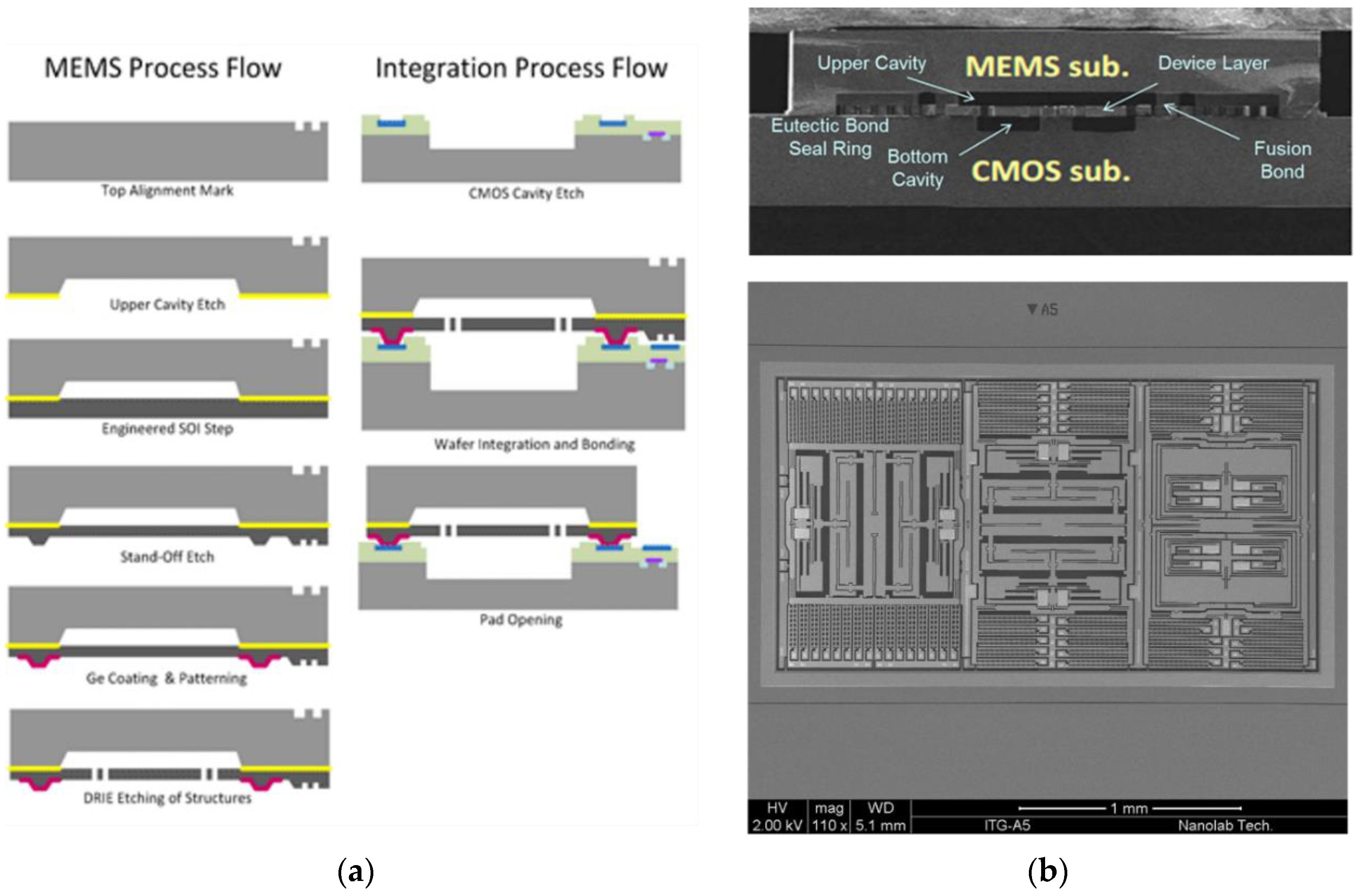

Sensors | Free Full-Text | Wafer-Level Vacuum Packaging of Smart Sensors – #15

Sensors | Free Full-Text | Wafer-Level Vacuum Packaging of Smart Sensors – #15

China SiC Coated Graphite Barrel Susceptor Suppliers, Manufacturers – Advanced Customized SiC Coated Graphite Barrel Susceptor – Semicorex – #16

China SiC Coated Graphite Barrel Susceptor Suppliers, Manufacturers – Advanced Customized SiC Coated Graphite Barrel Susceptor – Semicorex – #16

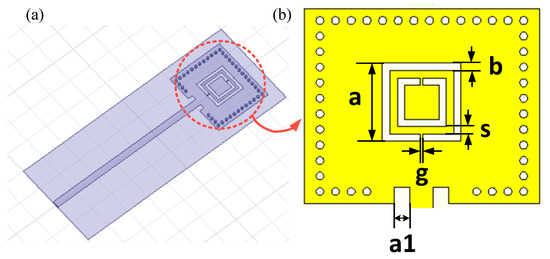

Micromachines | Free Full-Text | A Microwave Pressure Sensor Loaded with Complementary Split Ring Resonator for High-Temperature Applications – #17

Micromachines | Free Full-Text | A Microwave Pressure Sensor Loaded with Complementary Split Ring Resonator for High-Temperature Applications – #17

EP0742580A2 – Barrier seal for electrostatic chuck – Google Patents – #18

EP0742580A2 – Barrier seal for electrostatic chuck – Google Patents – #18

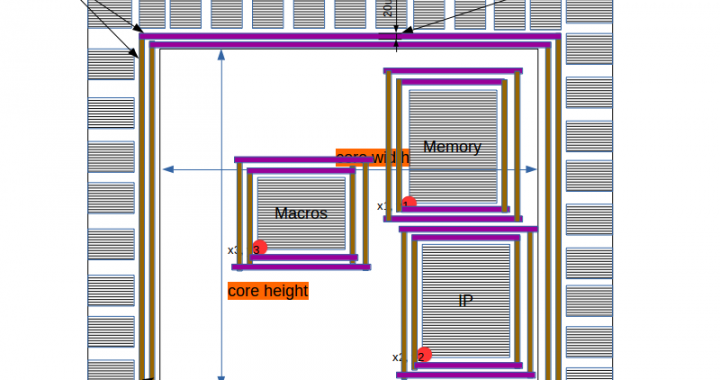

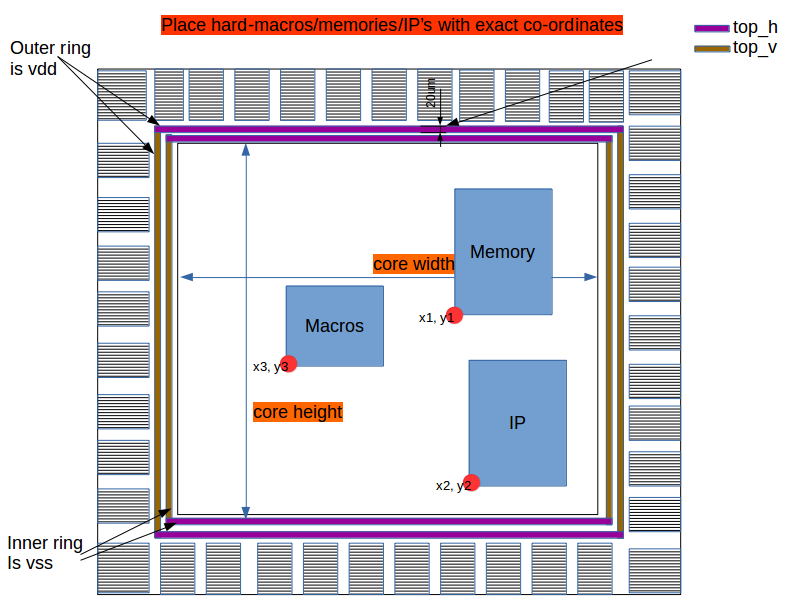

Mentor Graphics ASIC Design Flow – #19

Mentor Graphics ASIC Design Flow – #19

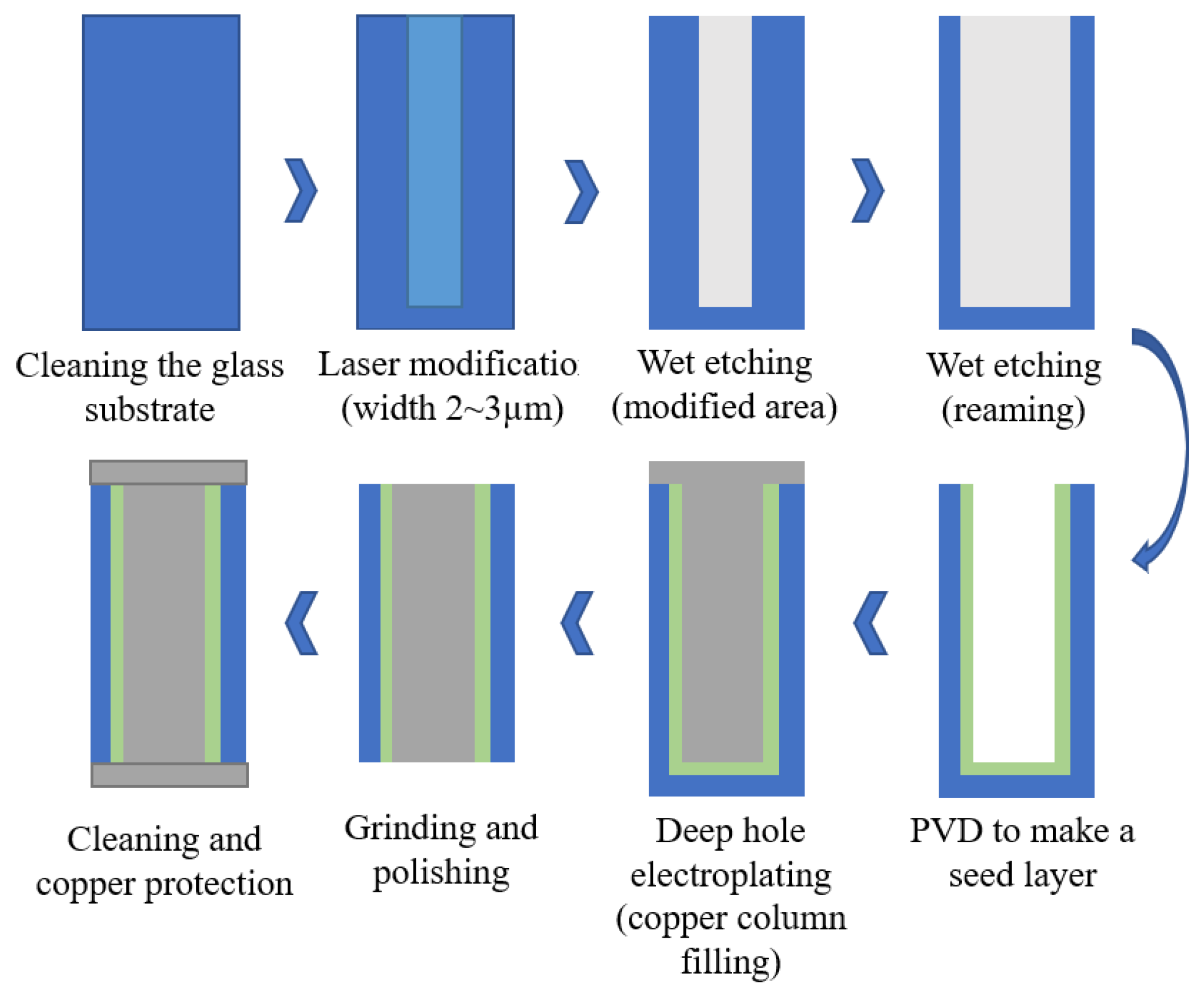

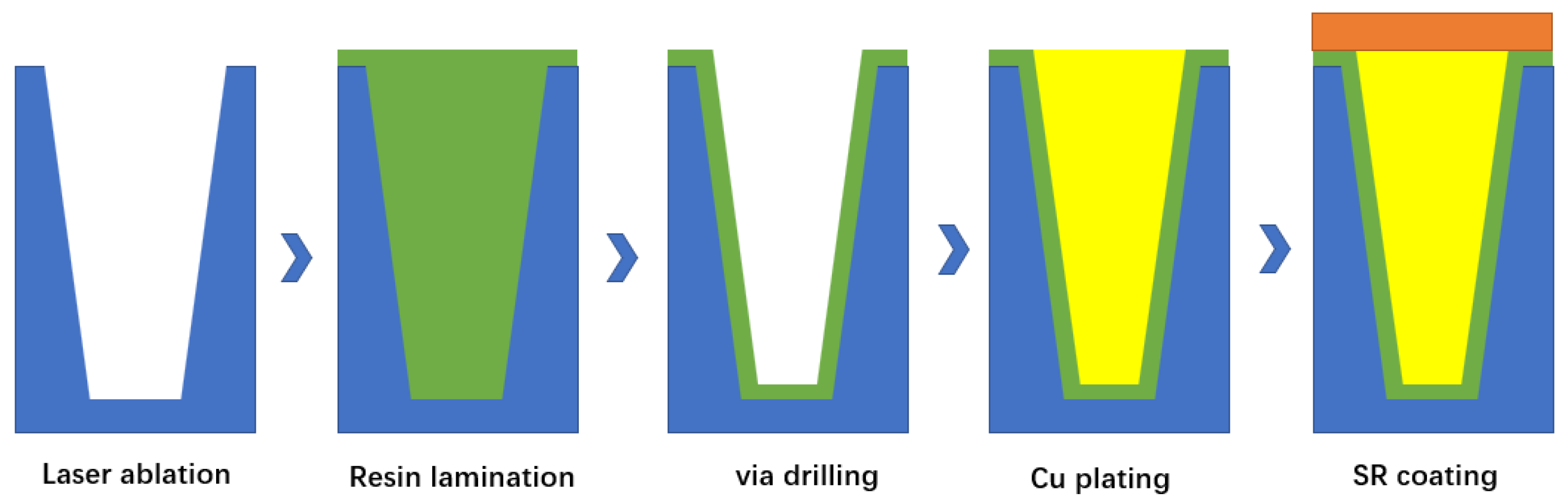

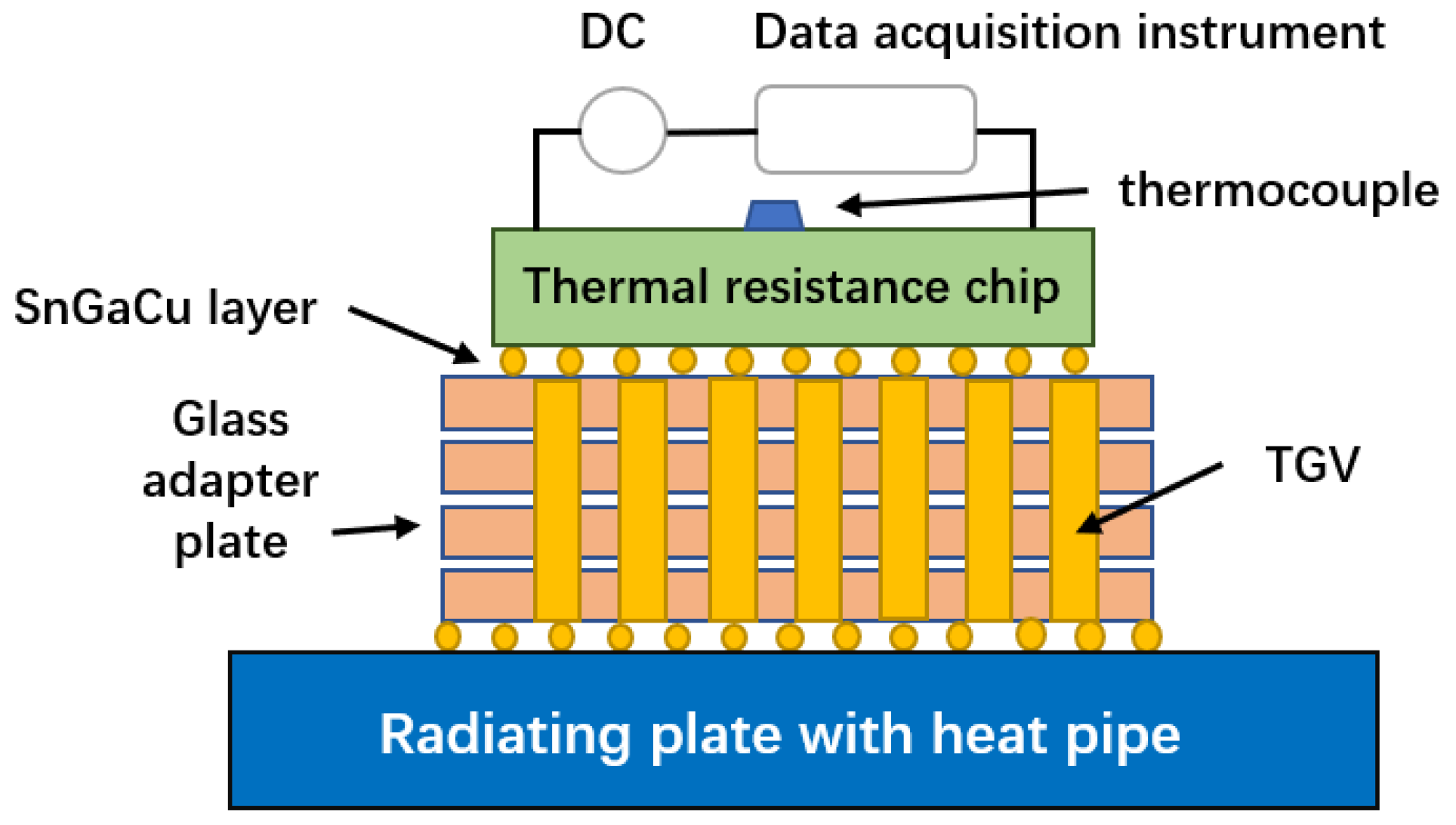

TCV and TGV Technology | Encyclopedia MDPI – #20

TCV and TGV Technology | Encyclopedia MDPI – #20

Summary of helium leak rate detected after corrosion test. | Download Scientific Diagram – #21

Summary of helium leak rate detected after corrosion test. | Download Scientific Diagram – #21

Fabrication process flow. (a) Si deep trench etching. (b) Deposited SiO… | Download Scientific Diagram – #22

Fabrication process flow. (a) Si deep trench etching. (b) Deposited SiO… | Download Scientific Diagram – #22

15: Die seal ring shorted to the power pads by the wedge bonds. | Download Scientific Diagram – #23

15: Die seal ring shorted to the power pads by the wedge bonds. | Download Scientific Diagram – #23

Design guideline for XC2000 and XE16x Micrcontroller board layout – #24

Design guideline for XC2000 and XE16x Micrcontroller board layout – #24

PPT – The common questions in analog layout PowerPoint Presentation, free download – ID:5517738 – #25

PPT – The common questions in analog layout PowerPoint Presentation, free download – ID:5517738 – #25

From design to tape-out in SCL 180nm CMOS integrated circuit fabrication technology – PDF Free Download – #26

From design to tape-out in SCL 180nm CMOS integrated circuit fabrication technology – PDF Free Download – #26

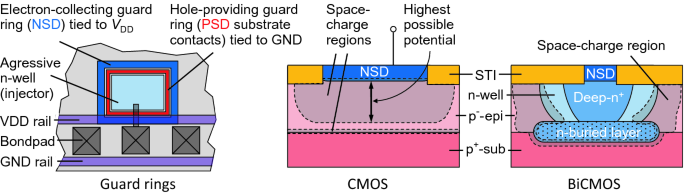

Digital VLSI Design Lecture 1: Introduction – #27

Digital VLSI Design Lecture 1: Introduction – #27

Electroplating IC Packages – #28

Electroplating IC Packages – #28

From Design to Tape-out in SCL 180 nm CMOS Integrated Circuit Fabrication Technology – #29

From Design to Tape-out in SCL 180 nm CMOS Integrated Circuit Fabrication Technology – #29

PAD RING CREATION | DRC CLEAN | VIRTUOSO (PART4) | PHYSICAL VERIFICATION | ASIC | VLSIFaB – YouTube – #30

PAD RING CREATION | DRC CLEAN | VIRTUOSO (PART4) | PHYSICAL VERIFICATION | ASIC | VLSIFaB – YouTube – #30

What are seal rings and their uses? – Quora – #31

What are seal rings and their uses? – Quora – #31

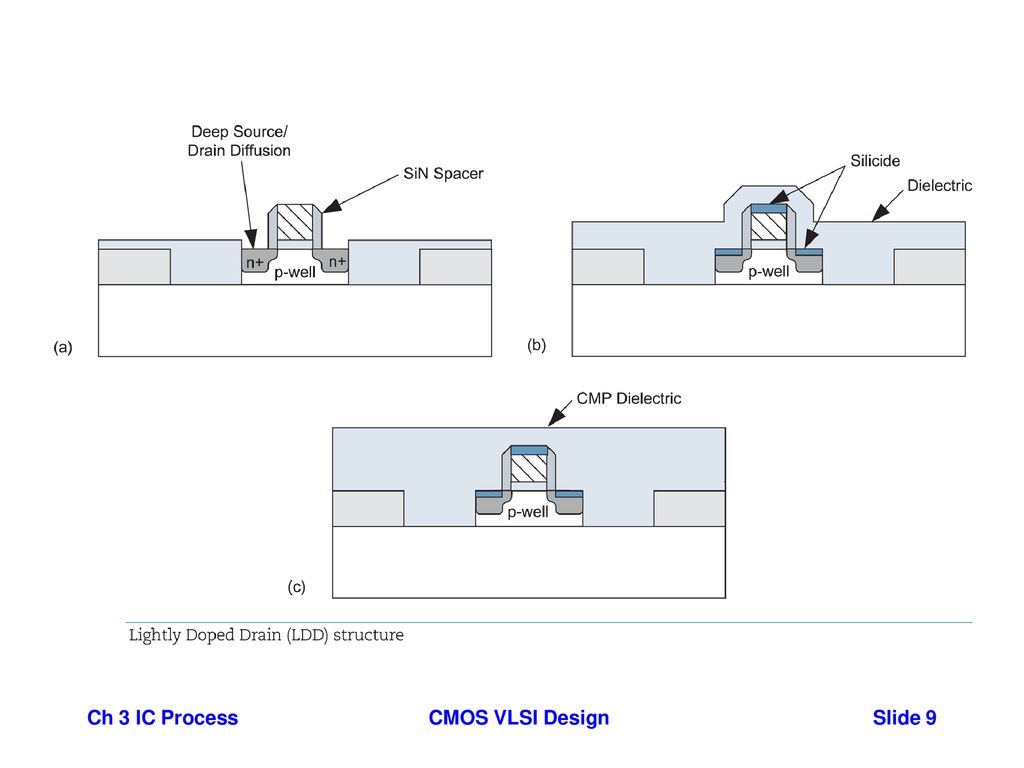

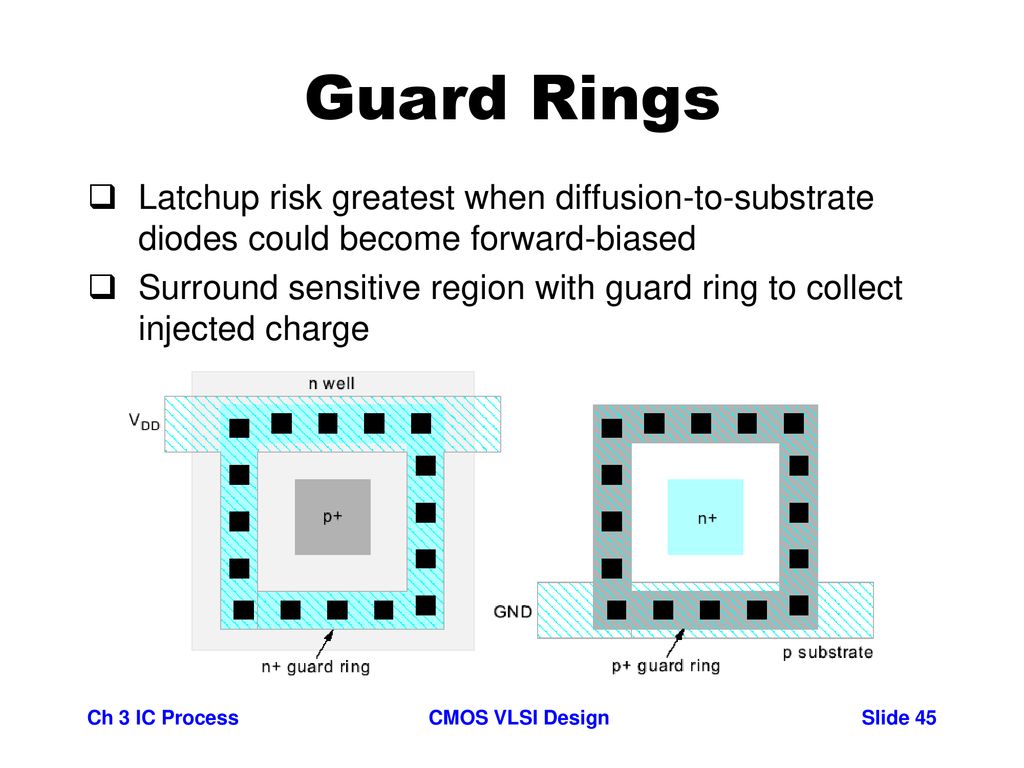

Introduction to CMOS VLSI Design Chapter 3: CMOS Processing Technology – ppt download – #32

Introduction to CMOS VLSI Design Chapter 3: CMOS Processing Technology – ppt download – #32

PDF) VLSI Design – #33

PDF) VLSI Design – #33

Design and performance of a cantilever piezoelectric power generation device for real-time road safety warnings – ScienceDirect – #34

Design and performance of a cantilever piezoelectric power generation device for real-time road safety warnings – ScienceDirect – #34

THIS DOCUMENT MAY NOT BE REPRODUCED OR COPIED IN WHOLE OR IN PART – #35

THIS DOCUMENT MAY NOT BE REPRODUCED OR COPIED IN WHOLE OR IN PART – #35

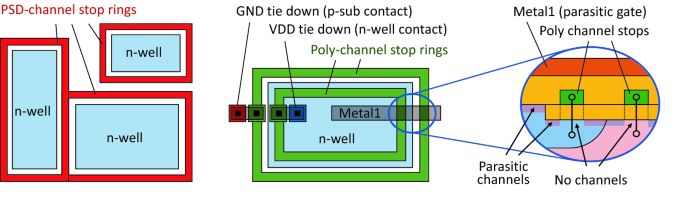

The CHIP – A Design Guide for Reducing Substrate Noise Coupling in RF Applications – #36

The CHIP – A Design Guide for Reducing Substrate Noise Coupling in RF Applications – #36

Micro- and Nanoelectronics – #37

Micro- and Nanoelectronics – #37

Parallel-Prefix Adder in Spin-Orbit Torque Magnetic RAM for High Bit-Width Non-Volatile Computation – #38

Parallel-Prefix Adder in Spin-Orbit Torque Magnetic RAM for High Bit-Width Non-Volatile Computation – #38

CPI INVITED: Assessment of Optimized Process Quality and Reliability for Wafer level Applications – #39

CPI INVITED: Assessment of Optimized Process Quality and Reliability for Wafer level Applications – #39

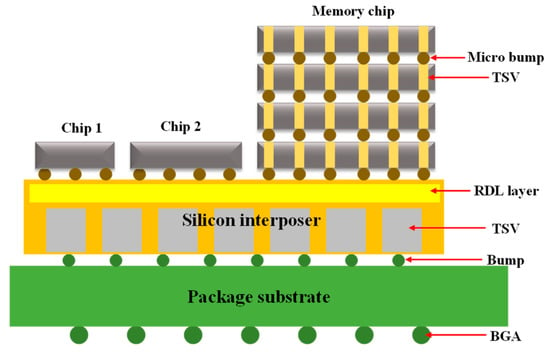

Micromachines | Free Full-Text | A Review of System-in-Package Technologies: Application and Reliability of Advanced Packaging – #40

Micromachines | Free Full-Text | A Review of System-in-Package Technologies: Application and Reliability of Advanced Packaging – #40

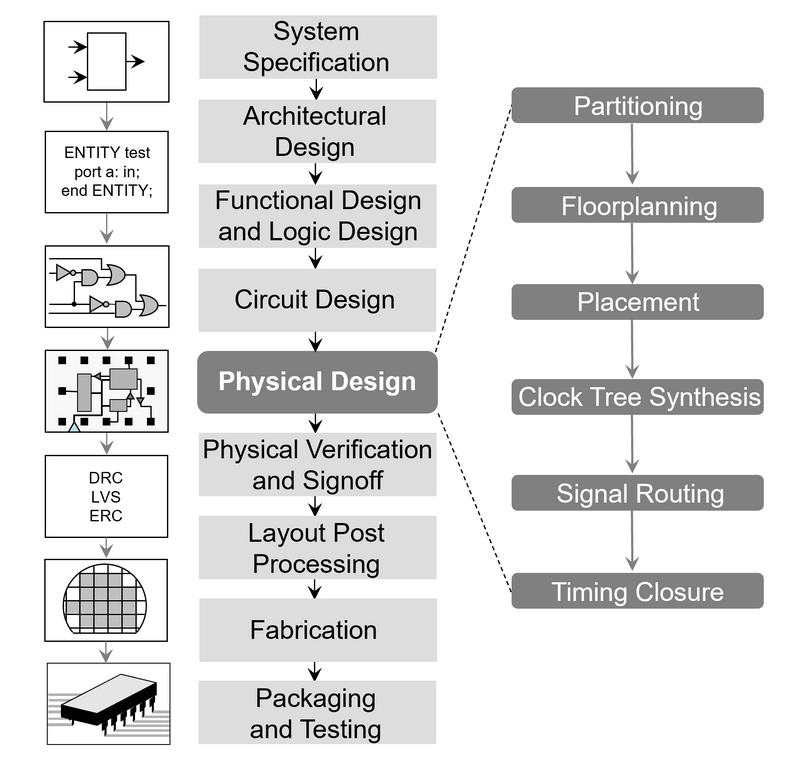

Physical design (electronics) – Wikipedia – #41

Physical design (electronics) – Wikipedia – #41

Research Article An Automatic Assembling System for Sealing Rings Based on Machine Vision – #42

Research Article An Automatic Assembling System for Sealing Rings Based on Machine Vision – #42

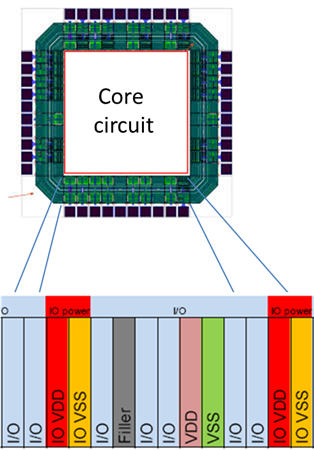

IO Ring Design PDF | PDF | Electrical Components | Electronics – #43

IO Ring Design PDF | PDF | Electrical Components | Electronics – #43

Mantra VLSI : November 2014 – #44

Mantra VLSI : November 2014 – #44

Custom College Class Ring, School Ring, Silver Graduation Ring, Gold Signet Ring, Personalized Ring, High School Class Ring, College Ring – Etsy – #45

Custom College Class Ring, School Ring, Silver Graduation Ring, Gold Signet Ring, Personalized Ring, High School Class Ring, College Ring – Etsy – #45

Figure 3 from Plasma inducted wafer arcing in back-end process and the impact on reliability | Semantic Scholar – #46

Figure 3 from Plasma inducted wafer arcing in back-end process and the impact on reliability | Semantic Scholar – #46

Surface-mountable capacitive tactile sensors with flipped CMOS-diaphragm on a flexible and stretchable bus line – ScienceDirect – #47

Surface-mountable capacitive tactile sensors with flipped CMOS-diaphragm on a flexible and stretchable bus line – ScienceDirect – #47

Vapor stem bubbles dominate heat transfer enhancement in extremely confined boiling – #48

Vapor stem bubbles dominate heat transfer enhancement in extremely confined boiling – #48

Encyclopedia of Packaging Materials, Processes, and Mechanics : Crystal Resonator Application – #49

Encyclopedia of Packaging Materials, Processes, and Mechanics : Crystal Resonator Application – #49

My plaque of ESD nuggets – #50

My plaque of ESD nuggets – #50

Analog Layout Design-Part Time – Part Time Analog Layout Design Training – Takshila VLSI – #51

Analog Layout Design-Part Time – Part Time Analog Layout Design Training – Takshila VLSI – #51

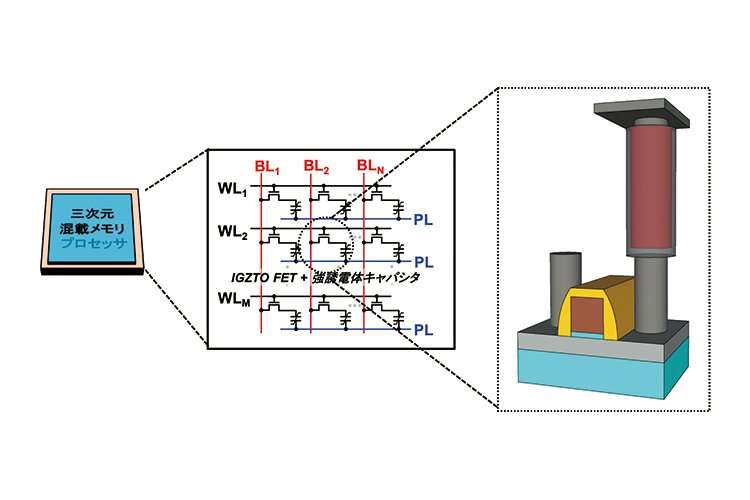

New hardware systems bring the future of artificial intelligence into view – #52

New hardware systems bring the future of artificial intelligence into view – #52

![PDF] Investigation on seal-ring rules for IC product reliability in 0.25-mum CMOS technology | Semantic Scholar PDF] Investigation on seal-ring rules for IC product reliability in 0.25-mum CMOS technology | Semantic Scholar](https://i.ytimg.com/vi/uY64LanMjAM/hq720.jpg?sqp\u003d-oaymwEhCK4FEIIDSFryq4qpAxMIARUAAAAAGAElAADIQj0AgKJD\u0026rs\u003dAOn4CLBa4RnOGtS29A0TmYaIFSzYW1n-PA) PDF] Investigation on seal-ring rules for IC product reliability in 0.25-mum CMOS technology | Semantic Scholar – #53

PDF] Investigation on seal-ring rules for IC product reliability in 0.25-mum CMOS technology | Semantic Scholar – #53

VLSI/VLSI/VLSI_labs/Tutorials/Tutorial_2/Inverter.cal/Inverter.drc.results at master · penatb/VLSI · GitHub – #54

VLSI/VLSI/VLSI_labs/Tutorials/Tutorial_2/Inverter.cal/Inverter.drc.results at master · penatb/VLSI · GitHub – #54

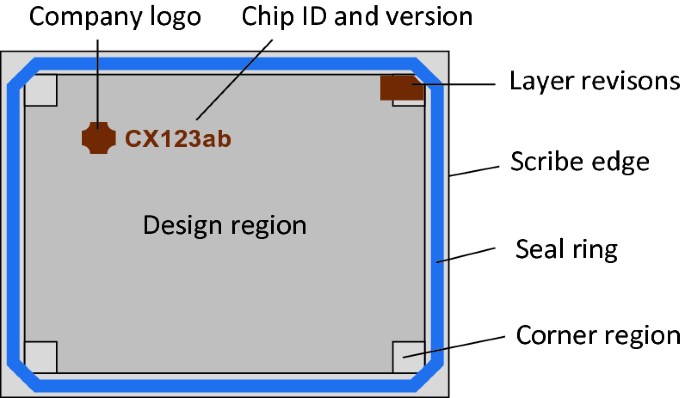

Chip Size 와 관련된 용어들 (chip size, seal ring, scribe lane) : 네이버 블로그 – #55

Chip Size 와 관련된 용어들 (chip size, seal ring, scribe lane) : 네이버 블로그 – #55

Design and layout strategies for integrated frequency synthesizers with high spectral purity | International Journal of Microwave and Wireless Technologies | Cambridge Core – #56

Design and layout strategies for integrated frequency synthesizers with high spectral purity | International Journal of Microwave and Wireless Technologies | Cambridge Core – #56

Guard rings: Structures, design methodology, integration, experimental results, and analysis for RF CMOS and RF mixed signal BiCMOS silicon germanium technology – ScienceDirect – #57

Guard rings: Structures, design methodology, integration, experimental results, and analysis for RF CMOS and RF mixed signal BiCMOS silicon germanium technology – ScienceDirect – #57

Odyssey of the charge pumping technique and its applications from micrometric- to atomic-scale era – #58

Odyssey of the charge pumping technique and its applications from micrometric- to atomic-scale era – #58

Roxtec Cable Entry Seal for Cabinets | PDF – #59

Roxtec Cable Entry Seal for Cabinets | PDF – #59

Analytics for US Patent No. 8242586, Integrated circuit chip with seal ring structure – #60

Analytics for US Patent No. 8242586, Integrated circuit chip with seal ring structure – #60

Seal Ring DRC error | Forum for Electronics – #61

Seal Ring DRC error | Forum for Electronics – #61

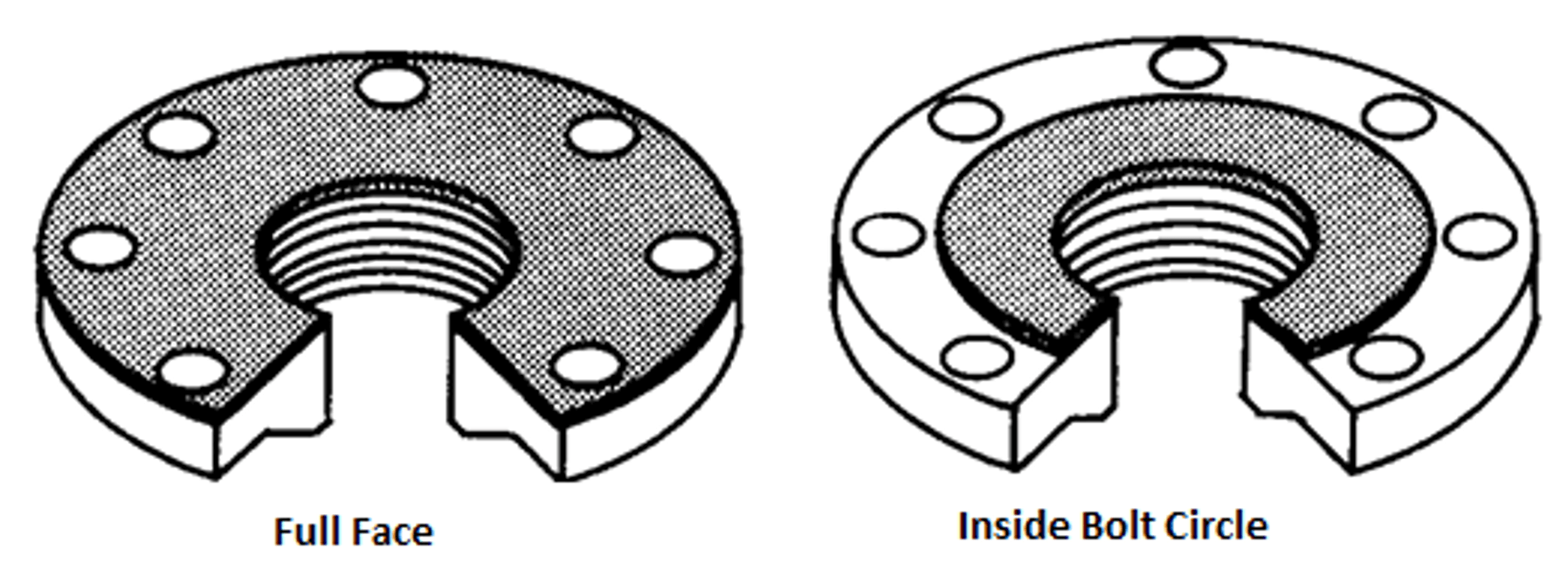

What is a Gasket? Types of Gaskets Used in Piping – #62

What is a Gasket? Types of Gaskets Used in Piping – #62

Materials, Fabrication and Characterization Methods | SpringerLink – #63

Materials, Fabrication and Characterization Methods | SpringerLink – #63

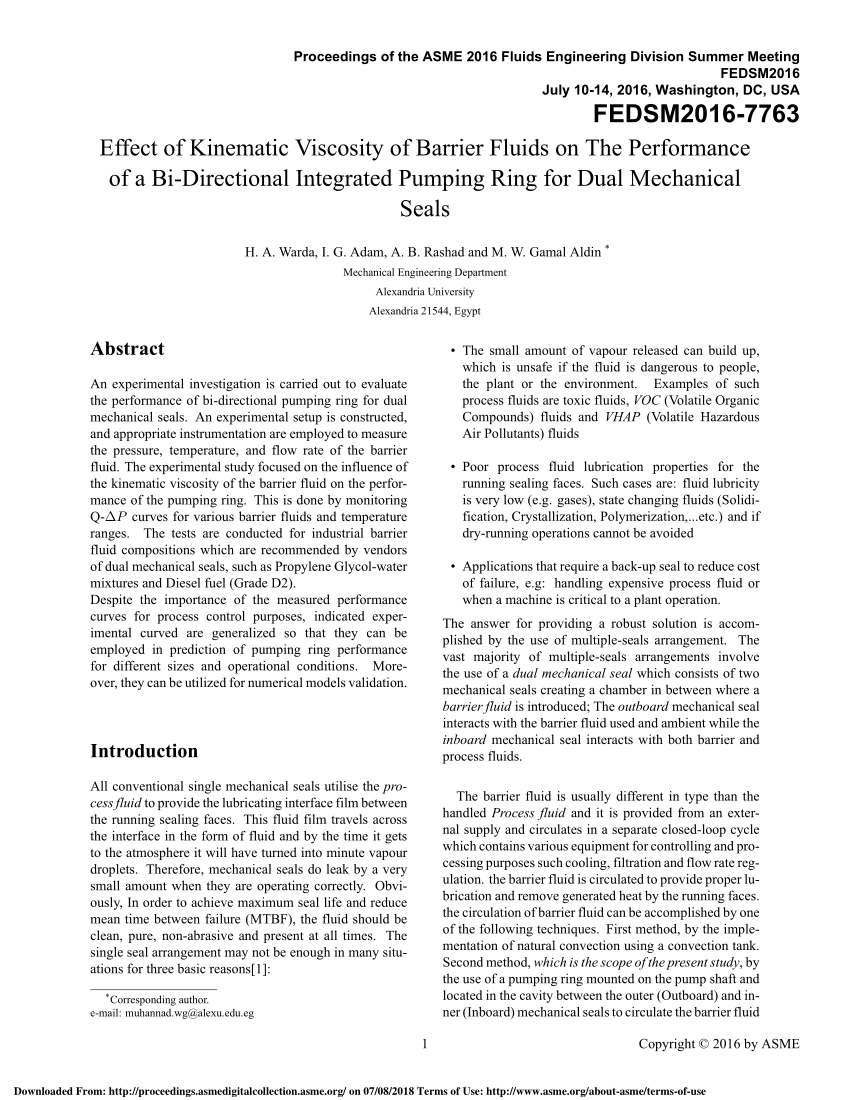

PDF) Effect of Kinematic Viscosity of Barrier Fluids on the Performance of a Bi-Directional Integrated Pumping Ring for Dual Mechanical Seals – #64

PDF) Effect of Kinematic Viscosity of Barrier Fluids on the Performance of a Bi-Directional Integrated Pumping Ring for Dual Mechanical Seals – #64

Analog layout – Wells, Taps, and Guard rings | Pulsic – #65

Analog layout – Wells, Taps, and Guard rings | Pulsic – #65

VLSI Full Syllabus | PDF | Mosfet | Computer Memory – #66

VLSI Full Syllabus | PDF | Mosfet | Computer Memory – #66

Encyclopedia of Packaging Materials, Processes, and Mechanics : PETEOS Oxide Fusion Bonding Assisted by a High-κ Dielectric Cap – #67

Encyclopedia of Packaging Materials, Processes, and Mechanics : PETEOS Oxide Fusion Bonding Assisted by a High-κ Dielectric Cap – #67

US10361201B2 – Semiconductor structure and device formed using selective epitaxial process – Google Patents – #68

US10361201B2 – Semiconductor structure and device formed using selective epitaxial process – Google Patents – #68

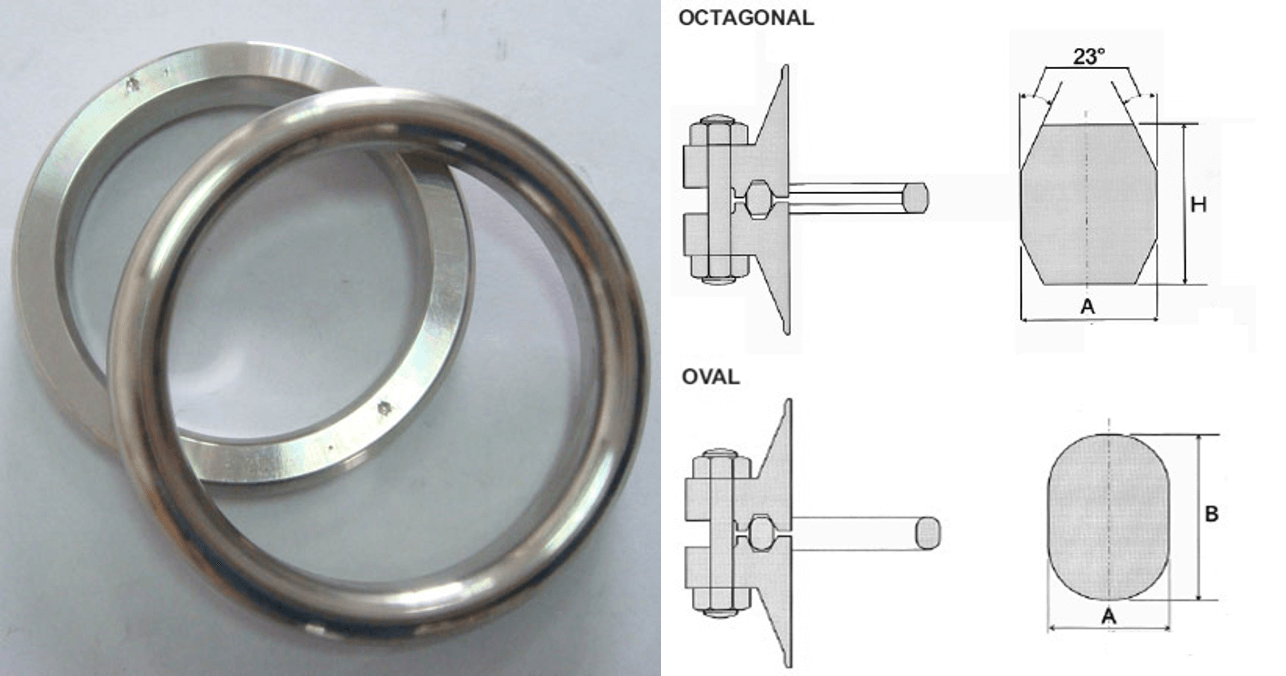

Ring Seal – an overview | ScienceDirect Topics – #69

Ring Seal – an overview | ScienceDirect Topics – #69

Introduction to Physical Design – AnySilicon – #70

Introduction to Physical Design – AnySilicon – #70

Inventorship Correction Affirmed for Patent on Intermodal Container for Transporting Gaseous Fluids | Patently-O – #71

Inventorship Correction Affirmed for Patent on Intermodal Container for Transporting Gaseous Fluids | Patently-O – #71

Impact of substrate resistance and layout on passivation etch-induced wafer arcing and reliability – ScienceDirect – #72

Impact of substrate resistance and layout on passivation etch-induced wafer arcing and reliability – ScienceDirect – #72

Figure 5 from Investigation on seal-ring rules for IC product reliability in 0.25-mum CMOS technology | Semantic Scholar – #73

Figure 5 from Investigation on seal-ring rules for IC product reliability in 0.25-mum CMOS technology | Semantic Scholar – #73

Microring laser sources – #74

Microring laser sources – #74

Schematics of the formation of sealed cavity for helium leak rate… | Download Scientific Diagram – #75

Schematics of the formation of sealed cavity for helium leak rate… | Download Scientific Diagram – #75

Integrated Circuit Design/Manufacturing – #76

Integrated Circuit Design/Manufacturing – #76

Sensors | Free Full-Text | A Study on the Thermomechanical Reliability Risks of Through-Silicon-Vias in Sensor Applications – #77

Sensors | Free Full-Text | A Study on the Thermomechanical Reliability Risks of Through-Silicon-Vias in Sensor Applications – #77

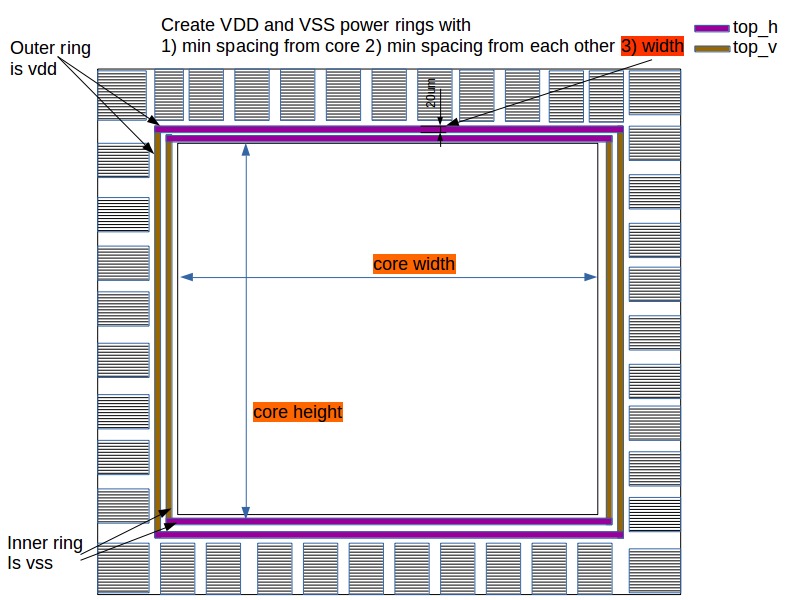

Investigation on seal-ring rules for IC product reliability in 0.25-μm CMOS technology – #78

Investigation on seal-ring rules for IC product reliability in 0.25-μm CMOS technology – #78

Revolutionize Your CNC Operations with the Rotoclear S3 Machine Vision System – #79

Revolutionize Your CNC Operations with the Rotoclear S3 Machine Vision System – #79

High Quality Factory source Gasket Ring – MAZDA Engine Valve cover gasket B3 KY01-10-235 – GS Seal Manufacturer and Supplier | GS Seal – #80

High Quality Factory source Gasket Ring – MAZDA Engine Valve cover gasket B3 KY01-10-235 – GS Seal Manufacturer and Supplier | GS Seal – #80

open-source-silicon #electric – #81

open-source-silicon #electric – #81

Encounter – VLSI Tutorial – #82

Encounter – VLSI Tutorial – #82

Detected helium leak rate of Cu-to-Cu thermo-compression bonding at 300… | Download Table – #83

Detected helium leak rate of Cu-to-Cu thermo-compression bonding at 300… | Download Table – #83

What is difference between taps and guard ring in VLSI? – Quora – #84

What is difference between taps and guard ring in VLSI? – Quora – #84

CALIFORNIA STATE UNIVERSITY NORTHRIDGE A Complete ASIC Design Implementation of ASYNC-SDM Router from RTL to GDSII A graduate pr – #85

CALIFORNIA STATE UNIVERSITY NORTHRIDGE A Complete ASIC Design Implementation of ASYNC-SDM Router from RTL to GDSII A graduate pr – #85

Quality issues of high pin count fine pitch VLSI packages | Semantic Scholar – #86

Quality issues of high pin count fine pitch VLSI packages | Semantic Scholar – #86

Introduction: ESD protection concepts for I/Os – SOFICS – Solutions for ICs – #87

Introduction: ESD protection concepts for I/Os – SOFICS – Solutions for ICs – #87

Material Removal Techniques vlsi design……….. …………… | studies and analysis – #88

Material Removal Techniques vlsi design……….. …………… | studies and analysis – #88

Micromachines | Free Full-Text | Research of Vertical via Based on Silicon, Ceramic and Glass – #89

Micromachines | Free Full-Text | Research of Vertical via Based on Silicon, Ceramic and Glass – #89

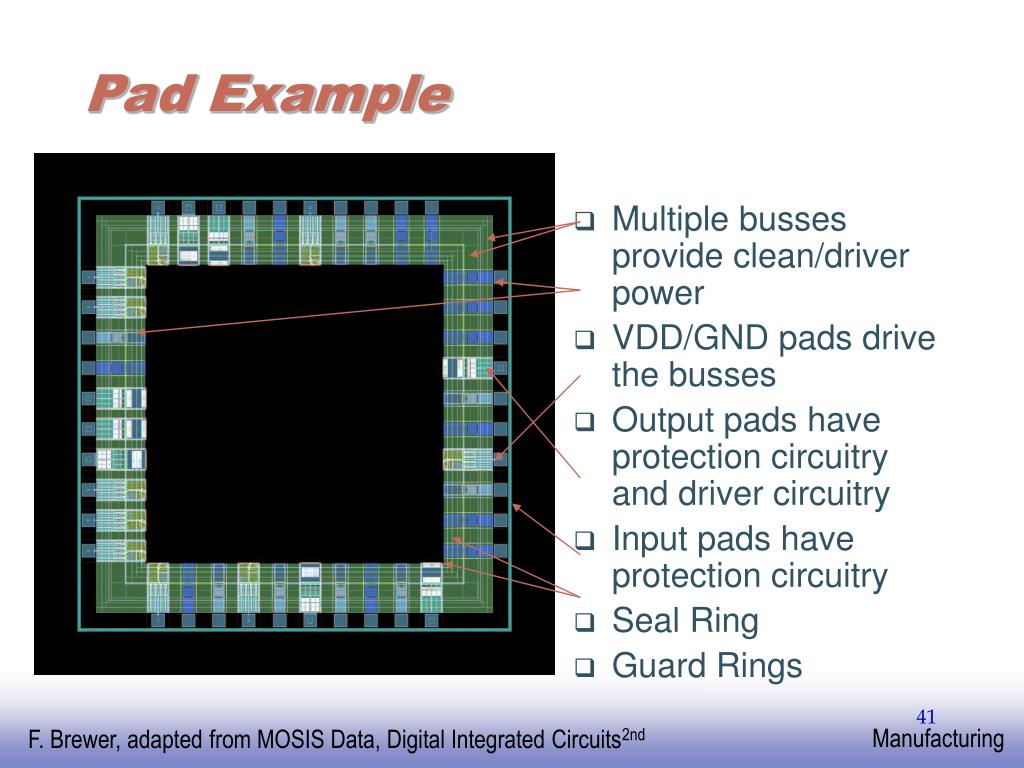

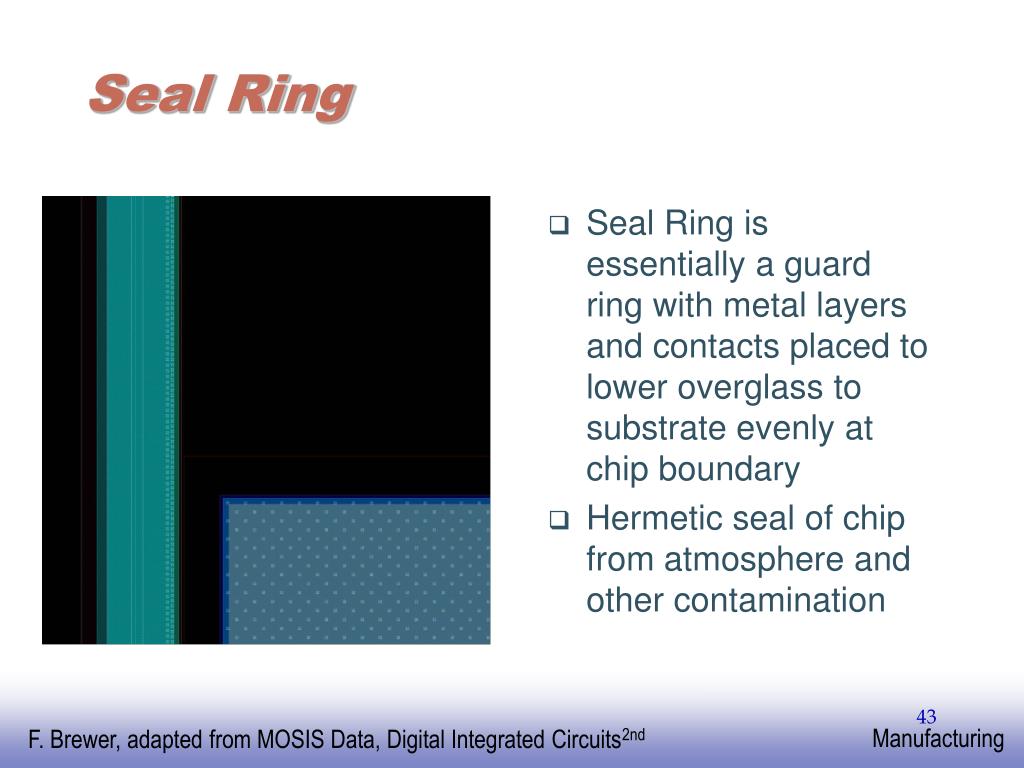

PPT – ECE 224a Process and Design Rules PowerPoint Presentation, free download – ID:3878530 – #90

PPT – ECE 224a Process and Design Rules PowerPoint Presentation, free download – ID:3878530 – #90

Gasket Seal Filter Housings for Bag-Out or Non … – Afri Air Ventilation – #91

Gasket Seal Filter Housings for Bag-Out or Non … – Afri Air Ventilation – #91

Department of Electrical Engineering Indian Institute of Technology, Delhi – #92

Department of Electrical Engineering Indian Institute of Technology, Delhi – #92

Hooman Reyhani on LinkedIn: #online #course #analog #mixedsignal #icdesign #semiconductors #ieee #sscs… – #93

Hooman Reyhani on LinkedIn: #online #course #analog #mixedsignal #icdesign #semiconductors #ieee #sscs… – #93

Putting it all together— Chip Level Issues – ppt video online download – #94

Putting it all together— Chip Level Issues – ppt video online download – #94

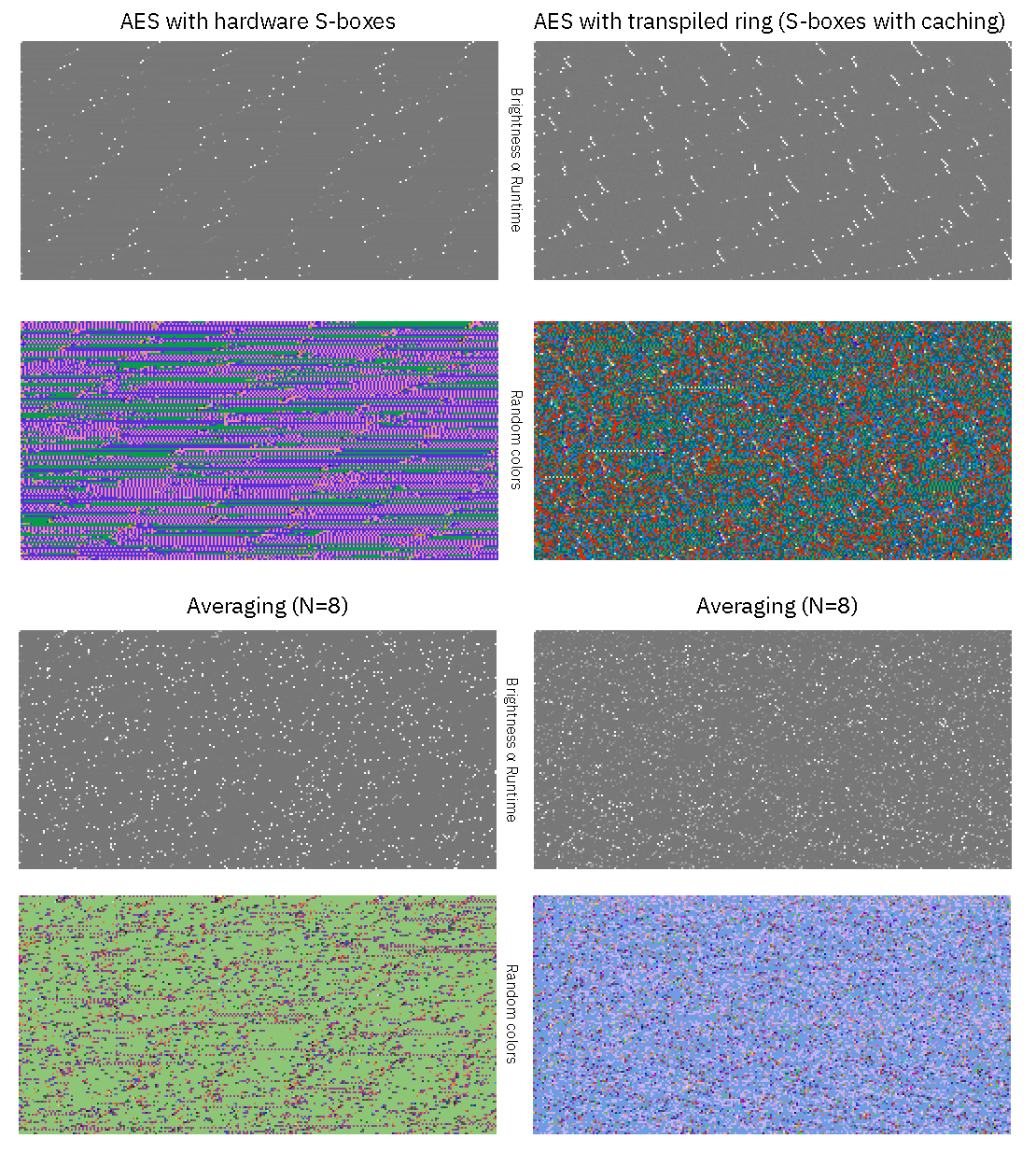

Runtime Trust Evaluation and Hardware Trojan Detection Using On-Chip EM Sensors – #95

Runtime Trust Evaluation and Hardware Trojan Detection Using On-Chip EM Sensors – #95

From design to tape-out in SCL 180nm CMOS integrated circuit fabrication technology – #96

From design to tape-out in SCL 180nm CMOS integrated circuit fabrication technology – #96

What is a guard ring? – Quora – #97

What is a guard ring? – Quora – #97

![PDF] Arithmetic logic UNIT (ALU) design using reconfigurable CMOS logic | Semantic Scholar PDF] Arithmetic logic UNIT (ALU) design using reconfigurable CMOS logic | Semantic Scholar](https://hardhatengineer.com/wp-content/uploads/2018/04/Gasket-tumbs.jpg) PDF] Arithmetic logic UNIT (ALU) design using reconfigurable CMOS logic | Semantic Scholar – #98

PDF] Arithmetic logic UNIT (ALU) design using reconfigurable CMOS logic | Semantic Scholar – #98

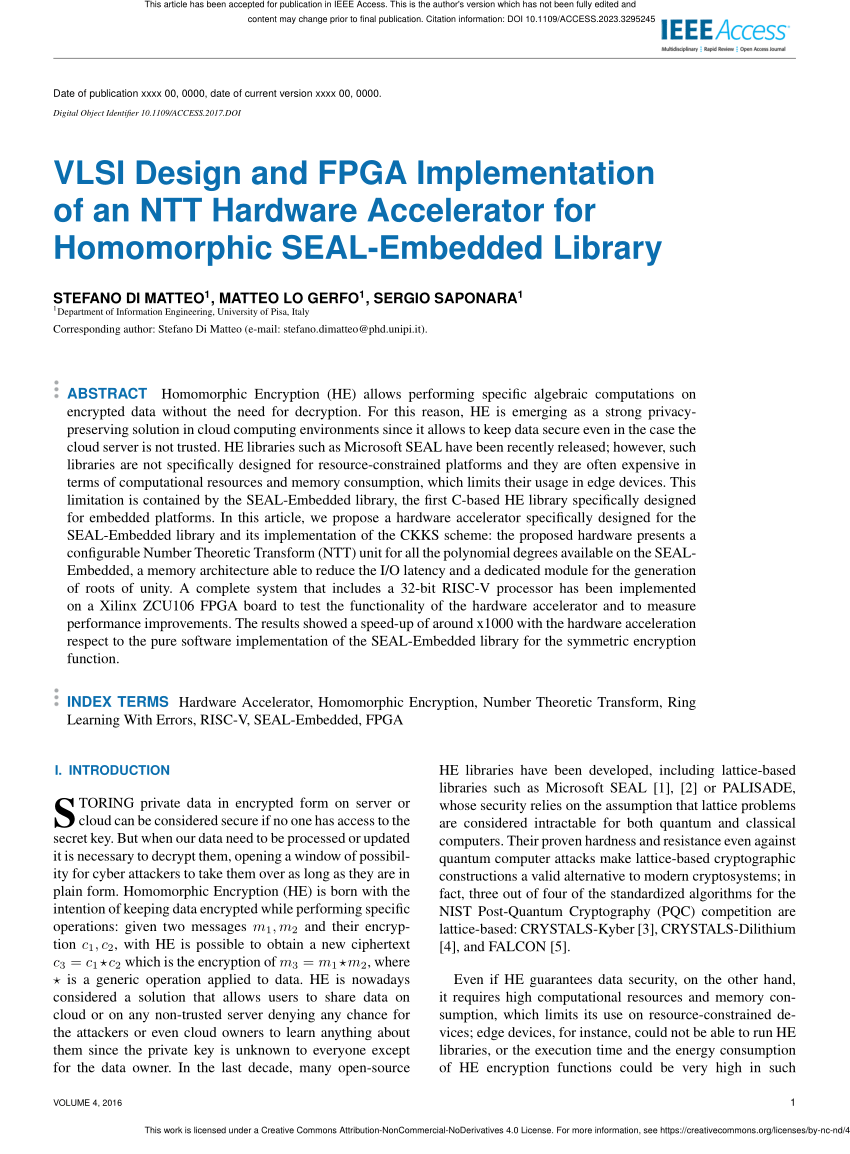

Think about pre-placed cells and power ring generation in opensource EDA – VLSI System Design – #99

Think about pre-placed cells and power ring generation in opensource EDA – VLSI System Design – #99

Addressing Reliability in Physical Design | SpringerLink – #100

Addressing Reliability in Physical Design | SpringerLink – #100

Analog Layout Training Institutes | Custom Layout Design Courses| Physical Verification and Analog IC Design Training | Takshila VLSI – #101

Analog Layout Training Institutes | Custom Layout Design Courses| Physical Verification and Analog IC Design Training | Takshila VLSI – #101

A Reliable I/O Ring For A Reliable SoC – #102

A Reliable I/O Ring For A Reliable SoC – #102

– #103

– #103

– #104

– #104

– #105

– #105

– #106

– #106

– #107

– #107

– #108

– #108

– #109

– #109

– #110

– #110

– #111

– #111

– #112

– #112

– #113

– #113

– #114

– #114

– #115

– #115

– #116

– #116

– #117

– #117

– #118

– #118

– #119

– #119

– #120

– #120

– #121

– #121

– #122

– #122

– #123

– #123

– #124

– #124

- seal ring semiconductor

- seal ring layout

- chip seal ring

– #125

– #125

– #126

– #126

Posts: seal ring in vlsi

Categories: Rings

Author: dienmayquynhon.com.vn