Discover 55+ guard ring layout technique super hot

Details images of guard ring layout technique by website dienmayquynhon.com.vn compilation. How to Minimize Parasitic Effects in IC Layout. Materials | Free Full-Text | Guard Ring Design to Prevent Edge Breakdown in Double-Diffused Planar InGaAs/InP Avalanche Photodiodes. Latch-up prevention in CMOS | Various techniques for latch-up prevention | Issues in Physical design – YouTube

High Holding Voltage SCR-LDMOS Stacking Structure With Ring-Resistance-Triggered Technique – #1

High Holding Voltage SCR-LDMOS Stacking Structure With Ring-Resistance-Triggered Technique – #1

Design of a 40 GHz low noise amplifier using multigate technique for cascode devices | Analog Integrated Circuits and Signal Processing – #2

Design of a 40 GHz low noise amplifier using multigate technique for cascode devices | Analog Integrated Circuits and Signal Processing – #2

eklakshya – #3

eklakshya – #3

- latch up circuit

- latch up protection circuit

- guard ring in vlsi

The 6 requirements of effective analog layout automation | Pulsic – #4

The 6 requirements of effective analog layout automation | Pulsic – #4

circuit analysis – What does “strap” mean in this context? – Electrical Engineering Stack Exchange – #5

circuit analysis – What does “strap” mean in this context? – Electrical Engineering Stack Exchange – #5

The investigation of the substrates noise suppression using guard rings in CMOS technology – #6

The investigation of the substrates noise suppression using guard rings in CMOS technology – #6

ECEN 474/704 Lab 3: Advanced Layout Techniques – #7

ECEN 474/704 Lab 3: Advanced Layout Techniques – #7

Homework_7 – #8

Homework_7 – #8

The Art and Science of Capacitive Technologies – Contract Engineering, Product Design & Development Company – Cardinal Peak – #9

The Art and Science of Capacitive Technologies – Contract Engineering, Product Design & Development Company – Cardinal Peak – #9

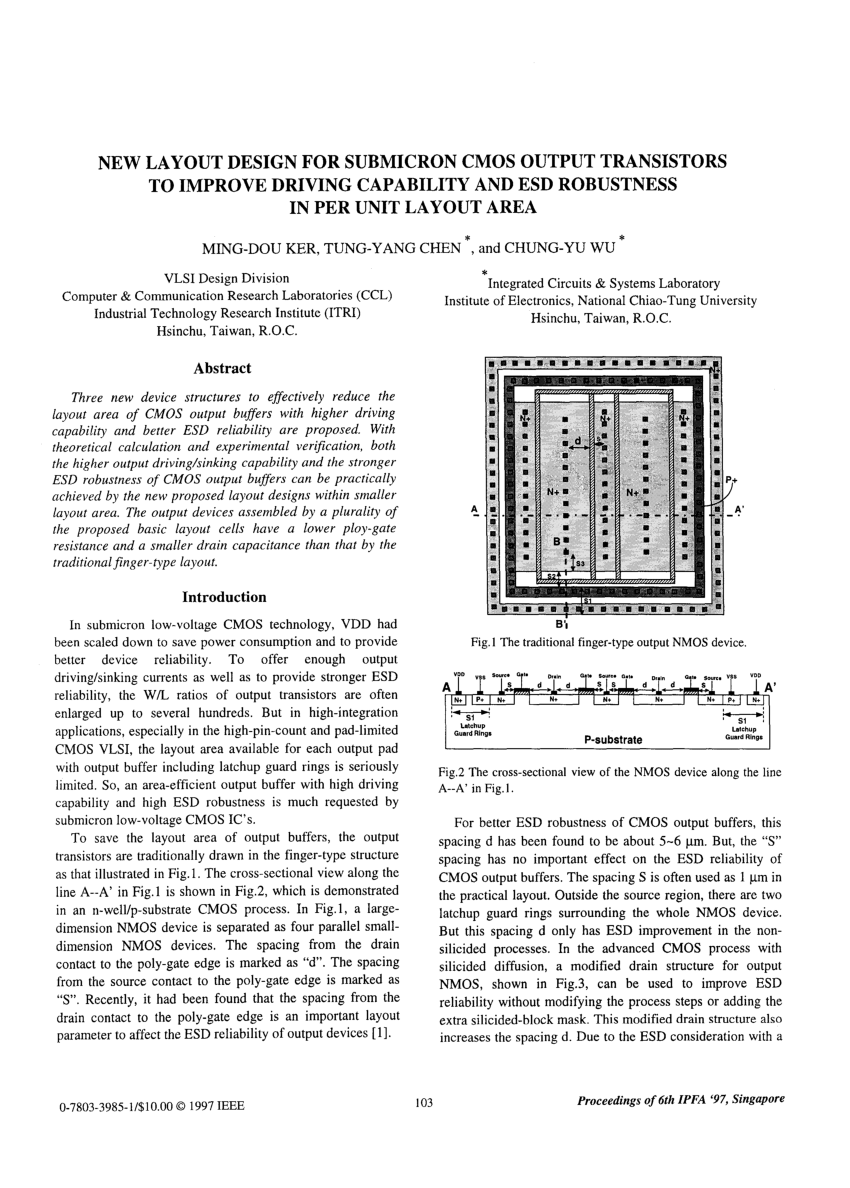

PDF) New layout design for submicron CMOS output transistors to improve driving capability and ESD robustness in per unit layout area – #10

PDF) New layout design for submicron CMOS output transistors to improve driving capability and ESD robustness in per unit layout area – #10

How to Route a PCB in KiCad | Sierra Circuits – #11

How to Route a PCB in KiCad | Sierra Circuits – #11

ekLakshya Innovation Labs | Hubli – #12

ekLakshya Innovation Labs | Hubli – #12

Memory Design Shift Left To Achieve Faster Development Turnaround Time – #13

Memory Design Shift Left To Achieve Faster Development Turnaround Time – #13

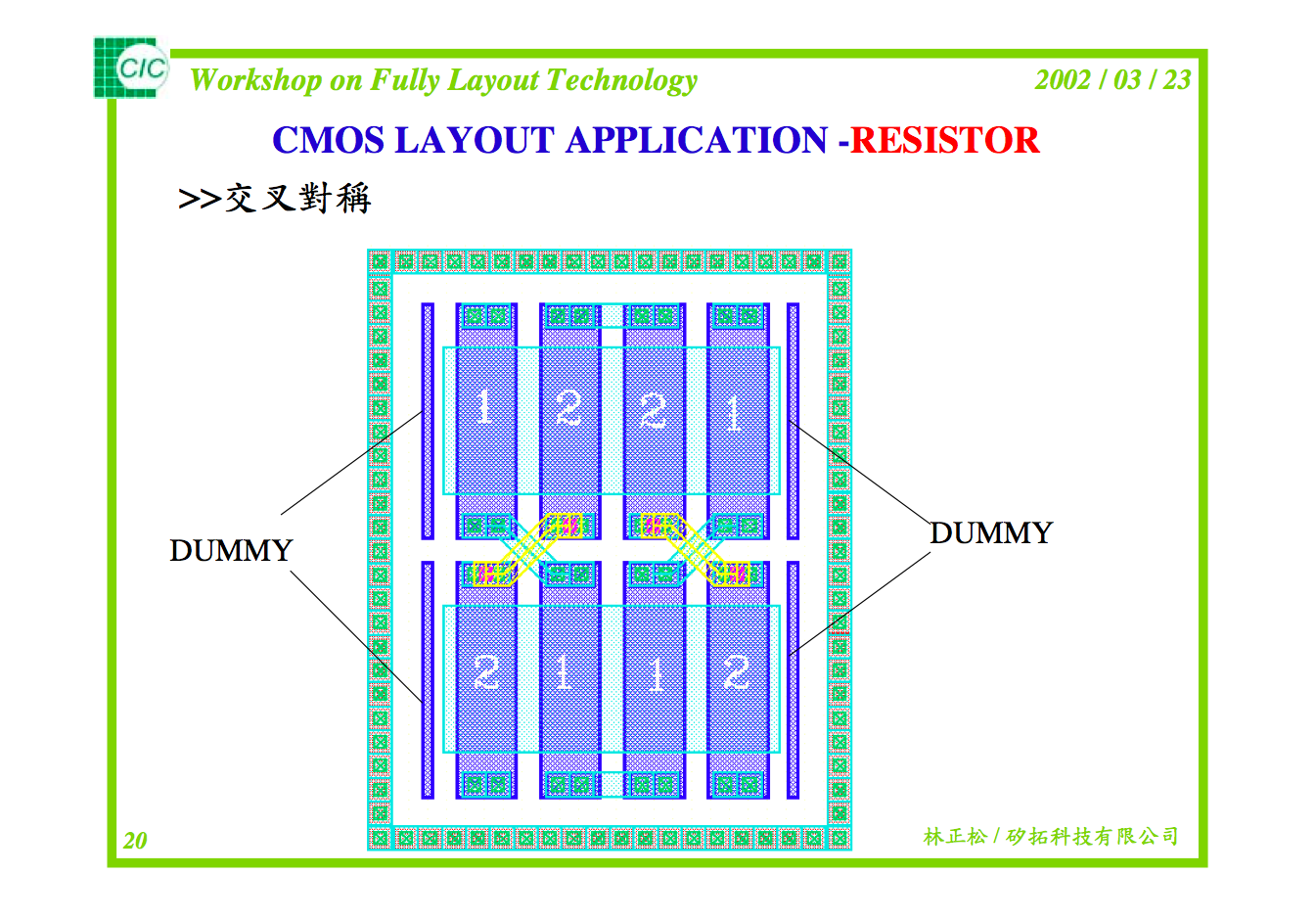

Errors due to process variations – ppt download – #14

Errors due to process variations – ppt download – #14

Latch-up prevention in CMOS | Various techniques for latch-up prevention | Issues in Physical design – YouTube – #15

Latch-up prevention in CMOS | Various techniques for latch-up prevention | Issues in Physical design – YouTube – #15

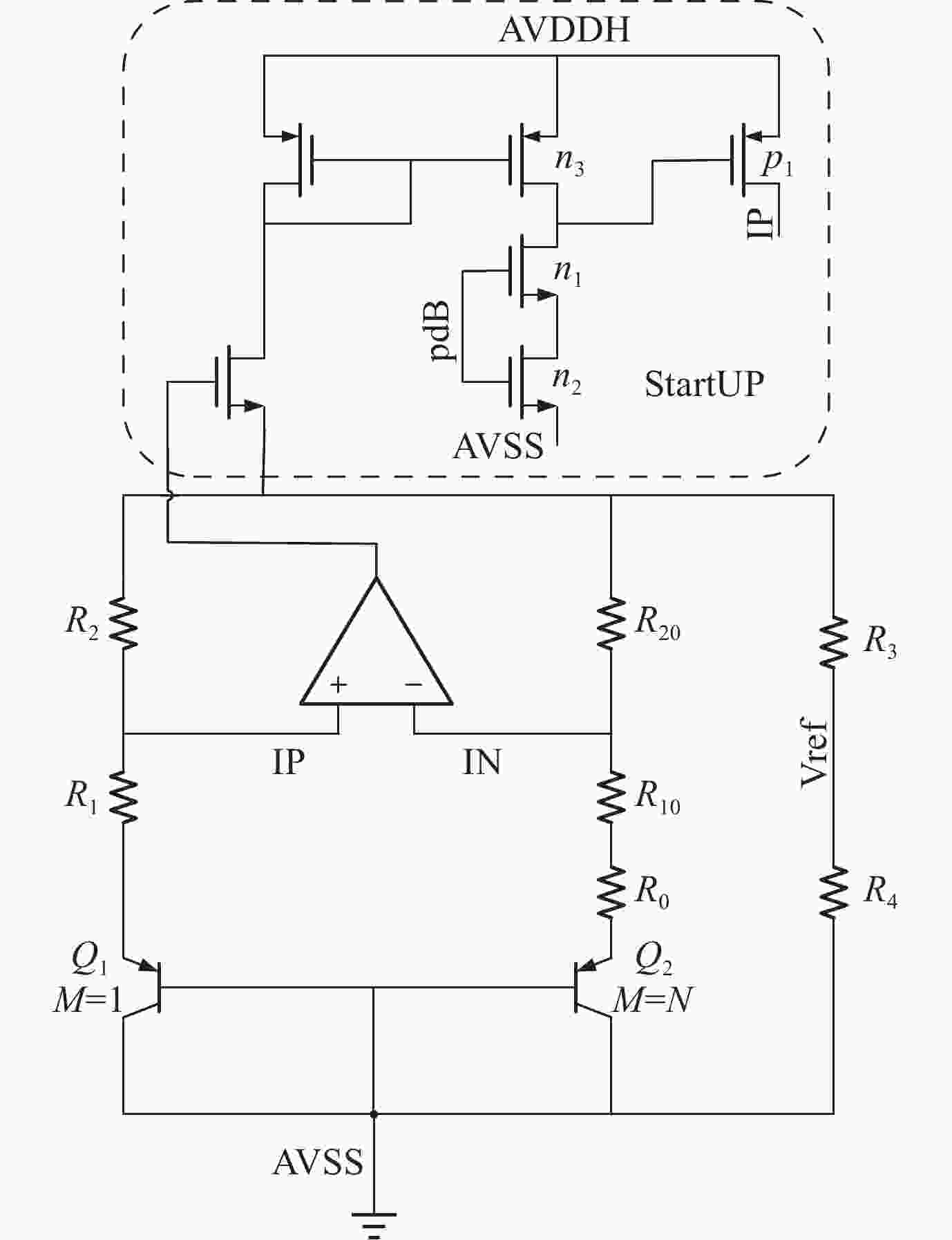

Technology Dependency of TID Response for a Custom Bandgap Voltage Reference in 65 nm to 28 nm Bulk CMOS Technologies – #16

Technology Dependency of TID Response for a Custom Bandgap Voltage Reference in 65 nm to 28 nm Bulk CMOS Technologies – #16

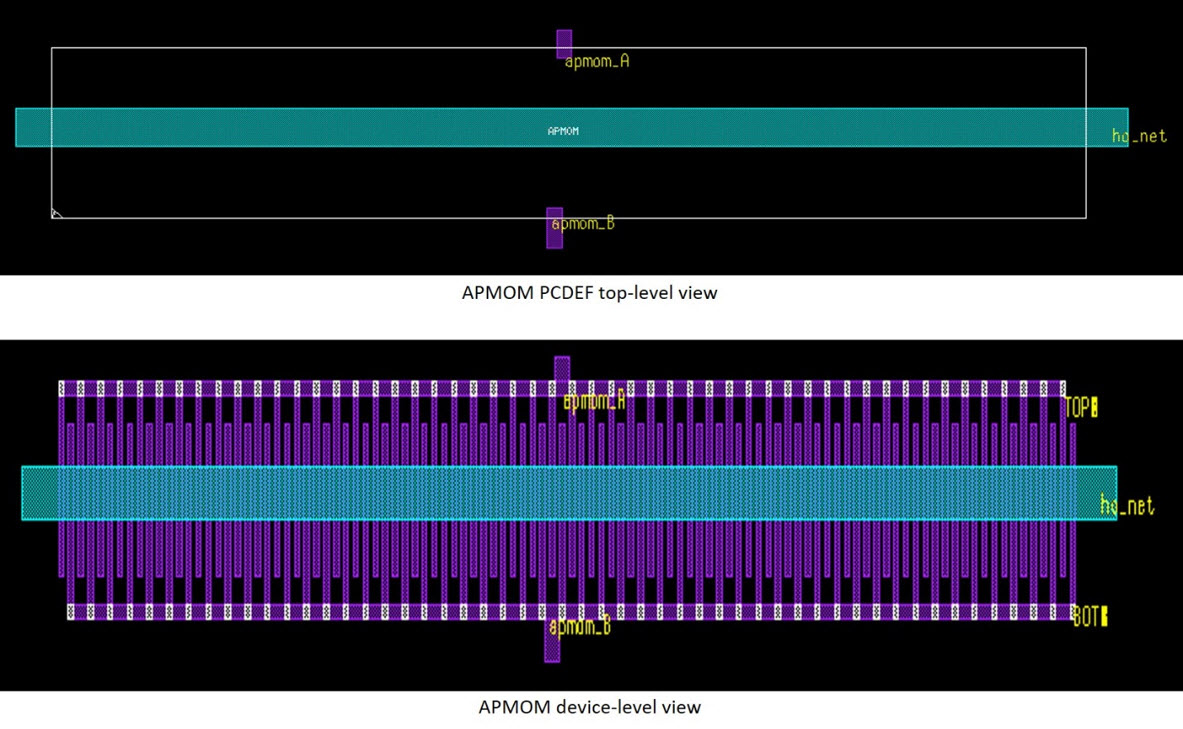

MIM/MOM capacitor extraction boosts analog and RF designs – Electrical Engineering News and Products – #17

MIM/MOM capacitor extraction boosts analog and RF designs – Electrical Engineering News and Products – #17

Advanced PCB Layout — FOCUS EMBEDDED – #18

Advanced PCB Layout — FOCUS EMBEDDED – #18

What is BGA Fanout Routing. Introduction | by Raymingpcb | Feb, 2024 | Medium – #19

What is BGA Fanout Routing. Introduction | by Raymingpcb | Feb, 2024 | Medium – #19

VSD-Physical-Verification-Using-Sky130/README.md at main · Avnish21/VSD-Physical-Verification-Using-Sky130 · GitHub – #20

VSD-Physical-Verification-Using-Sky130/README.md at main · Avnish21/VSD-Physical-Verification-Using-Sky130 · GitHub – #20

- double guard ring

- pcb guard ring

- pcb guard trace

Op-Amp Noise Reduction and Analysis Techniques – #21

Op-Amp Noise Reduction and Analysis Techniques – #21

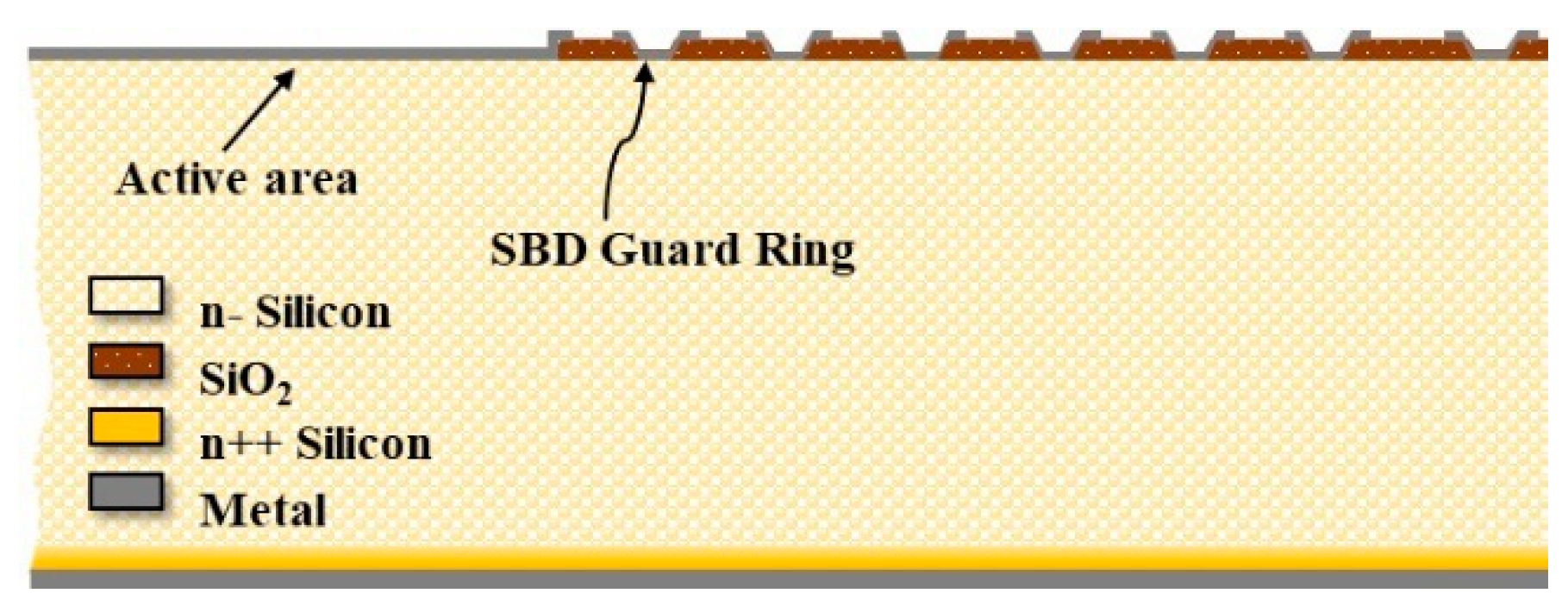

Figure 2 from Design, Fabrication, and Characterization of Ni/4H-SiC (0001) Schottky Diodes Array Equipped With Field Plate and Floating Guard Ring Edge Termination Structures | Semantic Scholar – #22

Figure 2 from Design, Fabrication, and Characterization of Ni/4H-SiC (0001) Schottky Diodes Array Equipped With Field Plate and Floating Guard Ring Edge Termination Structures | Semantic Scholar – #22

Driven guard – Wikipedia – #23

Driven guard – Wikipedia – #23

How to Minimize Parasitic Effects in IC Layout – #24

How to Minimize Parasitic Effects in IC Layout – #24

An overview of substrate noise reduction techniques – Quality Electronic Design, 2004. Proceedings. 5th International Symposium – #25

An overview of substrate noise reduction techniques – Quality Electronic Design, 2004. Proceedings. 5th International Symposium – #25

Electrostatic discharge protection patented technology retrieval search results – Eureka | Patsnap – #26

Electrostatic discharge protection patented technology retrieval search results – Eureka | Patsnap – #26

What Are Inlay Rings + Complete guide – Karen Handmade – #27

What Are Inlay Rings + Complete guide – Karen Handmade – #27

ADA4530-1. Data Sheet. LAYOUT GUIDELINES PHYSICAL IMPLEMENTATION OF GUARDING. TECHNIQUES. GUARD RING. VOUT. GUARD. GND. GUARD PLANE – Datasheet ADA4530-1 Analog Devices, Revision: B – #28

ADA4530-1. Data Sheet. LAYOUT GUIDELINES PHYSICAL IMPLEMENTATION OF GUARDING. TECHNIQUES. GUARD RING. VOUT. GUARD. GND. GUARD PLANE – Datasheet ADA4530-1 Analog Devices, Revision: B – #28

AN85951 PSoC™ 4 and PSoC™ 6 MCU CAPSENSE™ design guide – #29

AN85951 PSoC™ 4 and PSoC™ 6 MCU CAPSENSE™ design guide – #29

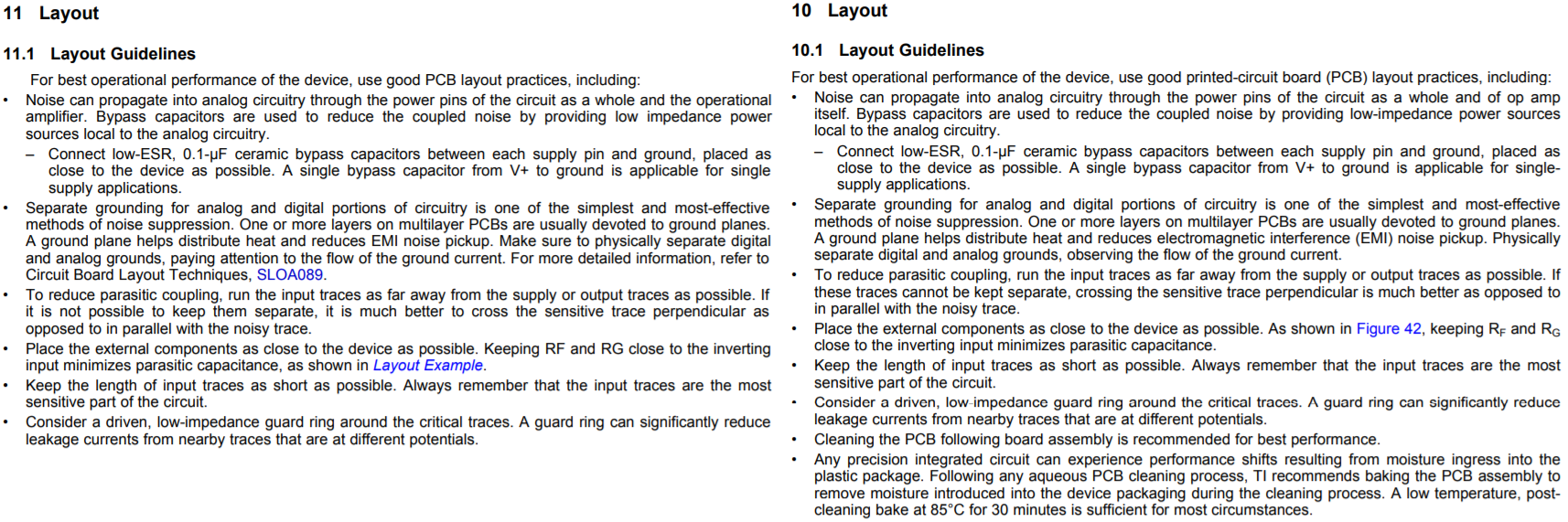

XTR117: Failing ESD Immunity test where TI’s TIPD126 design passes – Amplifiers forum – Amplifiers – TI E2E support forums – #30

XTR117: Failing ESD Immunity test where TI’s TIPD126 design passes – Amplifiers forum – Amplifiers – TI E2E support forums – #30

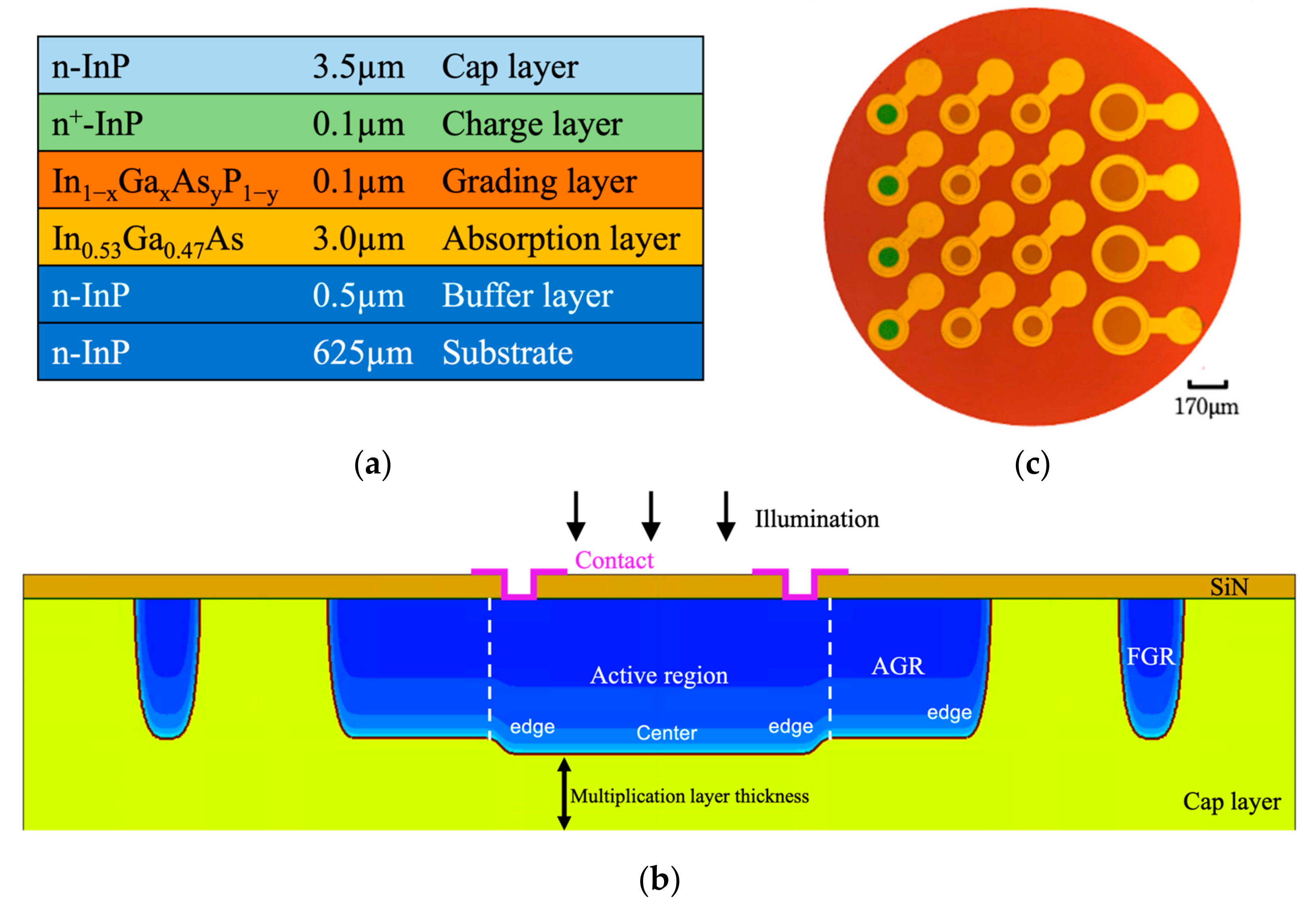

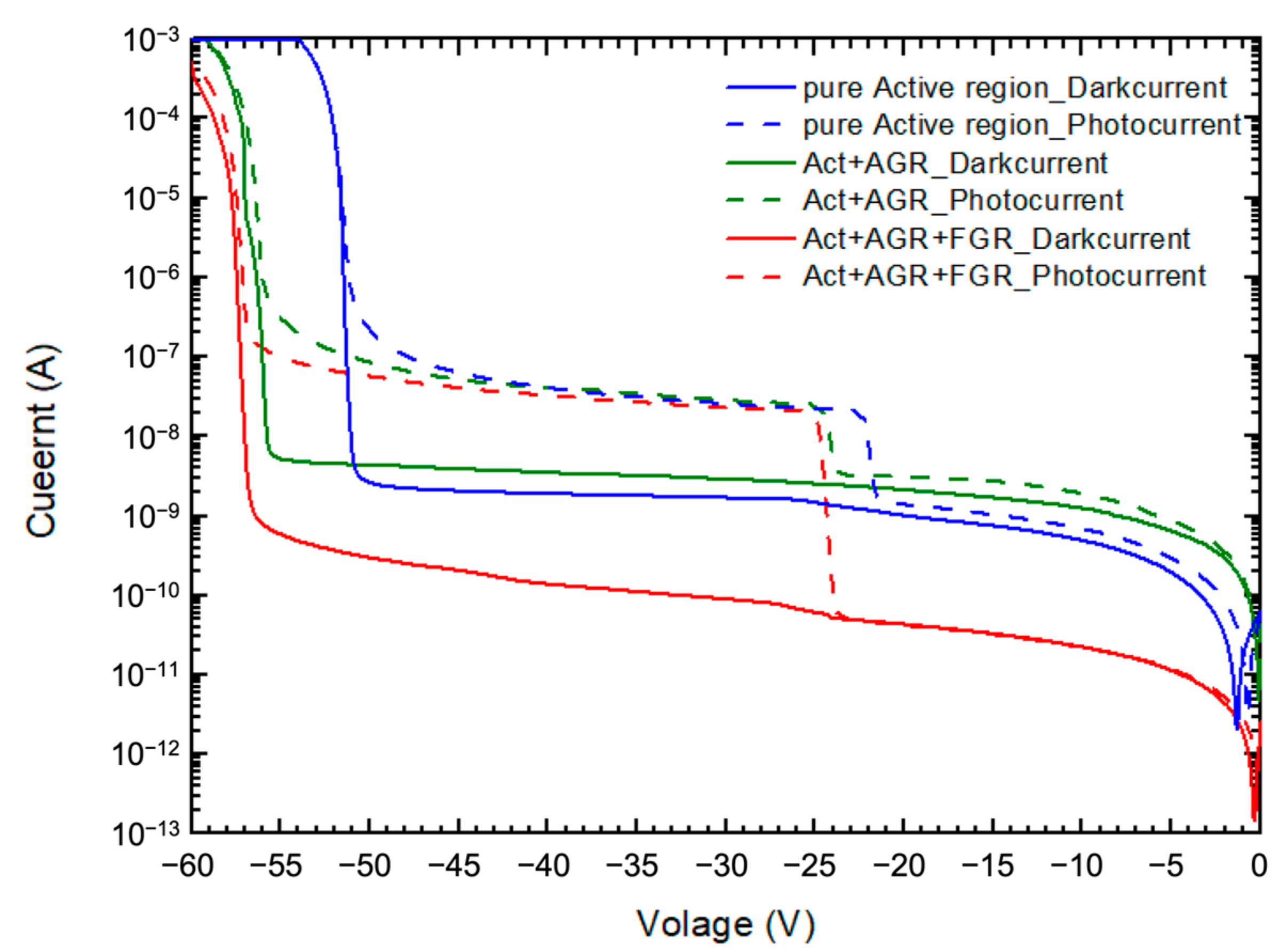

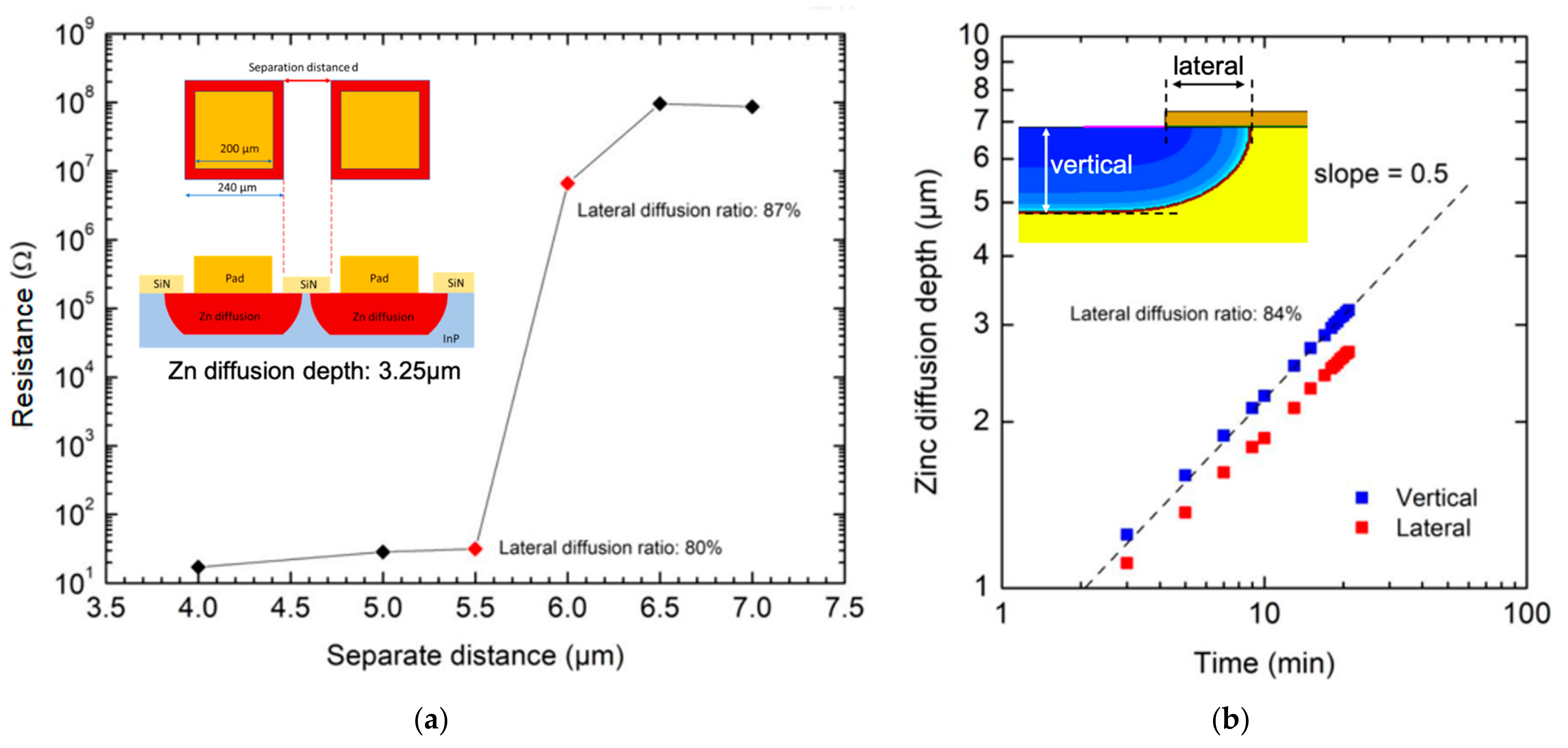

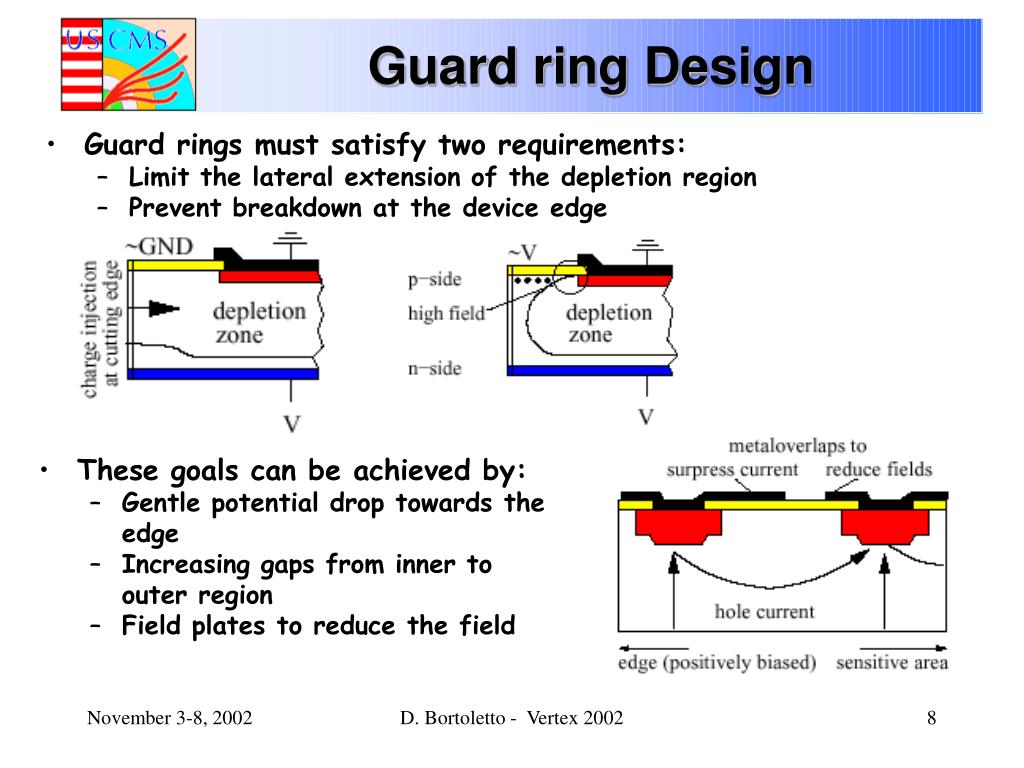

Materials | Free Full-Text | Guard Ring Design to Prevent Edge Breakdown in Double-Diffused Planar InGaAs/InP Avalanche Photodiodes – #31

Materials | Free Full-Text | Guard Ring Design to Prevent Edge Breakdown in Double-Diffused Planar InGaAs/InP Avalanche Photodiodes – #31

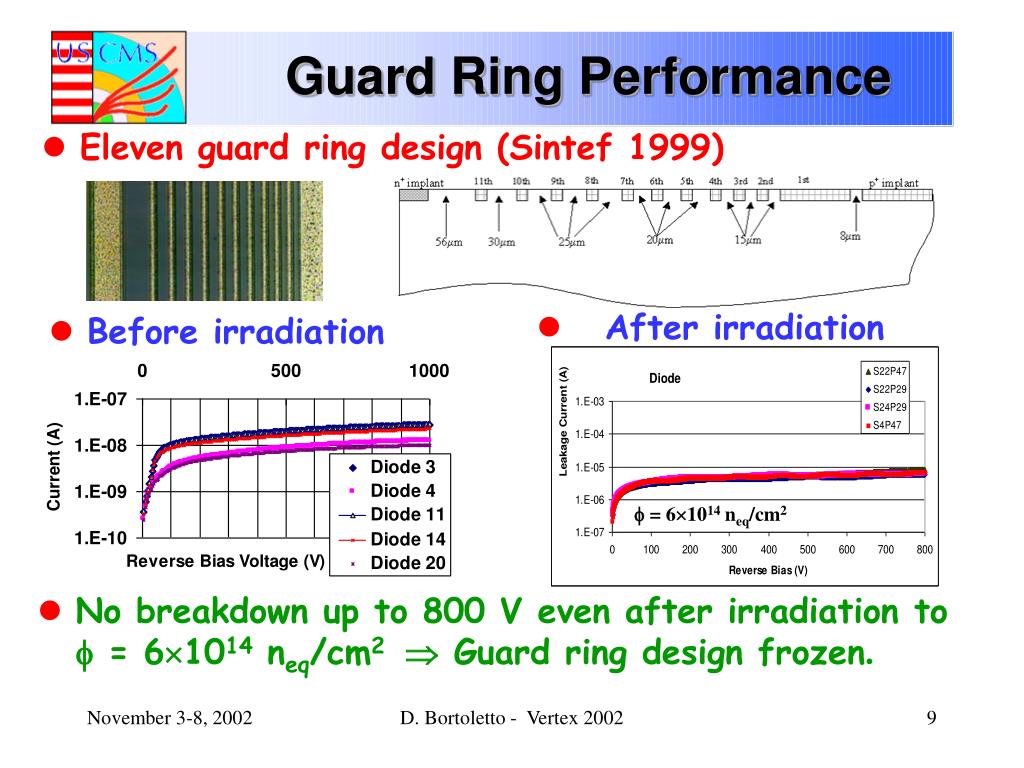

Recent Progress on 3D Silicon Detectors – CERN Document Server – #32

Recent Progress on 3D Silicon Detectors – CERN Document Server – #32

Optimizing isolated PCB design for EMC | Video | TI.com – #33

Optimizing isolated PCB design for EMC | Video | TI.com – #33

The Best PCB Design Guidelines for Reduced EMI | Advanced PCB Design Blog | Cadence – #34

The Best PCB Design Guidelines for Reduced EMI | Advanced PCB Design Blog | Cadence – #34

Double ring LR-PON protection: (a) Ring design (OCs shown in squares),… | Download Scientific Diagram – #35

Double ring LR-PON protection: (a) Ring design (OCs shown in squares),… | Download Scientific Diagram – #35

![PDF] Analysis of substrate noise suppression and latchup prevention in 90nm CMOS technology with 2-D simulation | Semantic Scholar PDF] Analysis of substrate noise suppression and latchup prevention in 90nm CMOS technology with 2-D simulation | Semantic Scholar](https://i.stack.imgur.com/v4iiH.png) PDF] Analysis of substrate noise suppression and latchup prevention in 90nm CMOS technology with 2-D simulation | Semantic Scholar – #36

PDF] Analysis of substrate noise suppression and latchup prevention in 90nm CMOS technology with 2-D simulation | Semantic Scholar – #36

- latch up guard ring

- driven guard

- latch up diagram

ADA4530-1. Data Sheet. LAYOUT GUIDELINES PHYSICAL IMPLEMENTATION OF GUARDING. TECHNIQUES. GUARD RING. VOUT. GUARD. GND. GUARD PLANE – Datasheet ADA4530-1 Analog Devices, 修订版: B – #37

ADA4530-1. Data Sheet. LAYOUT GUIDELINES PHYSICAL IMPLEMENTATION OF GUARDING. TECHNIQUES. GUARD RING. VOUT. GUARD. GND. GUARD PLANE – Datasheet ADA4530-1 Analog Devices, 修订版: B – #37

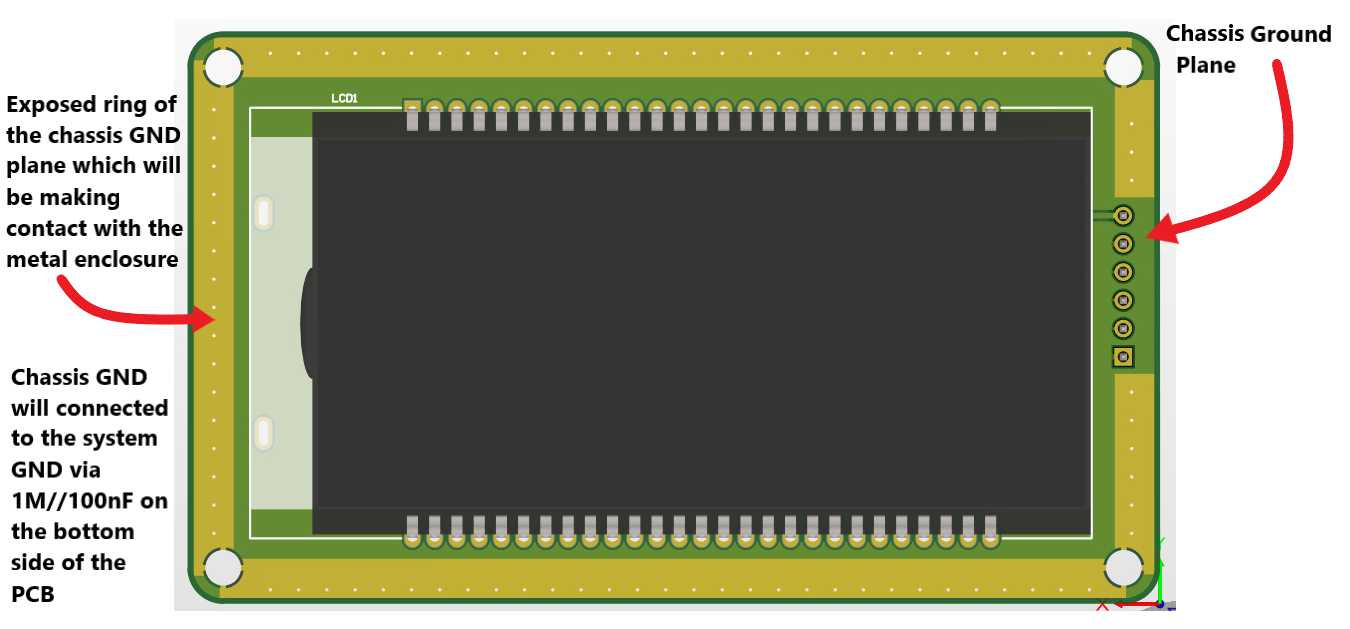

The Best PCB Grounding Techniques in Layout | Advanced PCB Design Blog | Cadence – #38

The Best PCB Grounding Techniques in Layout | Advanced PCB Design Blog | Cadence – #38

Many EMC Tips to Help You Design Better PCB Boards (with Keith Armstrong) – #39

Many EMC Tips to Help You Design Better PCB Boards (with Keith Armstrong) – #39

Audio Pcb Layout Techniques | Page 6 | diyAudio – #40

Audio Pcb Layout Techniques | Page 6 | diyAudio – #40

Study of the influence of virtual guard ring width on the performance of SPAD detectors in 180 nm standard CMOS technology – #41

Study of the influence of virtual guard ring width on the performance of SPAD detectors in 180 nm standard CMOS technology – #41

Democratization of The Nonlinear Harmonic Method for Turbomachinery – #42

Democratization of The Nonlinear Harmonic Method for Turbomachinery – #42

Figure 4 from Impact of guard ring layout on the stacked low-voltage PMOS for high-voltage ESD protection | Semantic Scholar – #43

Figure 4 from Impact of guard ring layout on the stacked low-voltage PMOS for high-voltage ESD protection | Semantic Scholar – #43

PCB design guidelines for the BlueNRG-1 and BlueNRG-2 devices – Application note – #44

PCB design guidelines for the BlueNRG-1 and BlueNRG-2 devices – Application note – #44

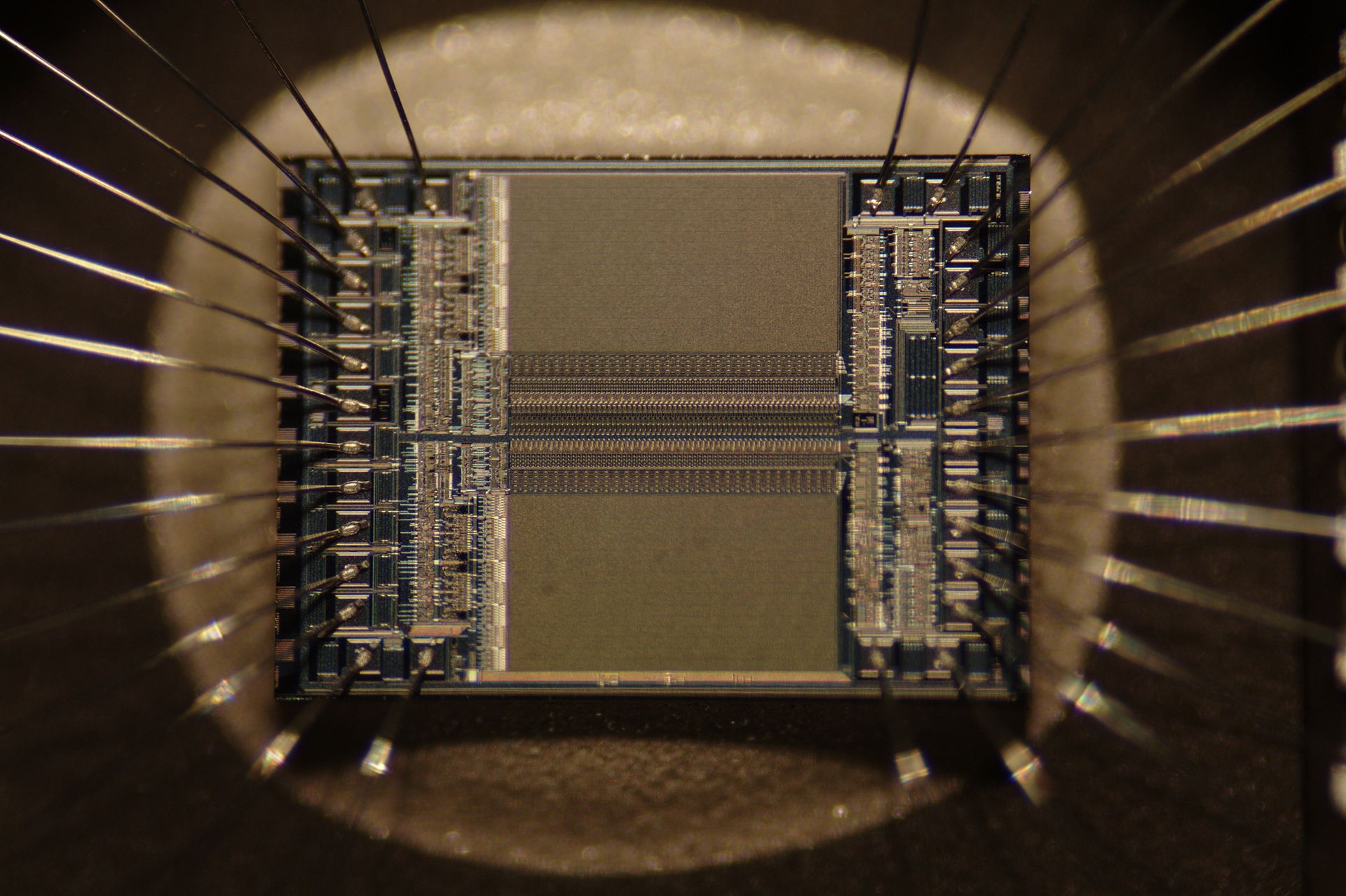

Sub)mm-wave Calibration – #45

Sub)mm-wave Calibration – #45

Physical design. (a) Interleaved layout of four MSFFs, each indicated… | Download Scientific Diagram – #46

Physical design. (a) Interleaved layout of four MSFFs, each indicated… | Download Scientific Diagram – #46

DNW Diode Extraction – Addition of Manual Guard Ring (Part-1) – YouTube – #47

DNW Diode Extraction – Addition of Manual Guard Ring (Part-1) – YouTube – #47

The 6 requirements of effective analog layout automation – #48

The 6 requirements of effective analog layout automation – #48

Microe IIb 07 08 PDF | PDF | Field Effect Transistor | Resistor – #49

Microe IIb 07 08 PDF | PDF | Field Effect Transistor | Resistor – #49

OPA1678: layout guide request – Audio forum – Audio – TI E2E support forums – #50

OPA1678: layout guide request – Audio forum – Audio – TI E2E support forums – #50

Analog Layout Techniques | PDF | Photolithography | Electronic Circuits – #51

Analog Layout Techniques | PDF | Photolithography | Electronic Circuits – #51

A new approach to analog layout – #52

A new approach to analog layout – #52

Latch-Up – #53

Latch-Up – #53

Analog Layout Design-Part Time – Part Time Analog Layout Design Training – Takshila VLSI – #54

Analog Layout Design-Part Time – Part Time Analog Layout Design Training – Takshila VLSI – #54

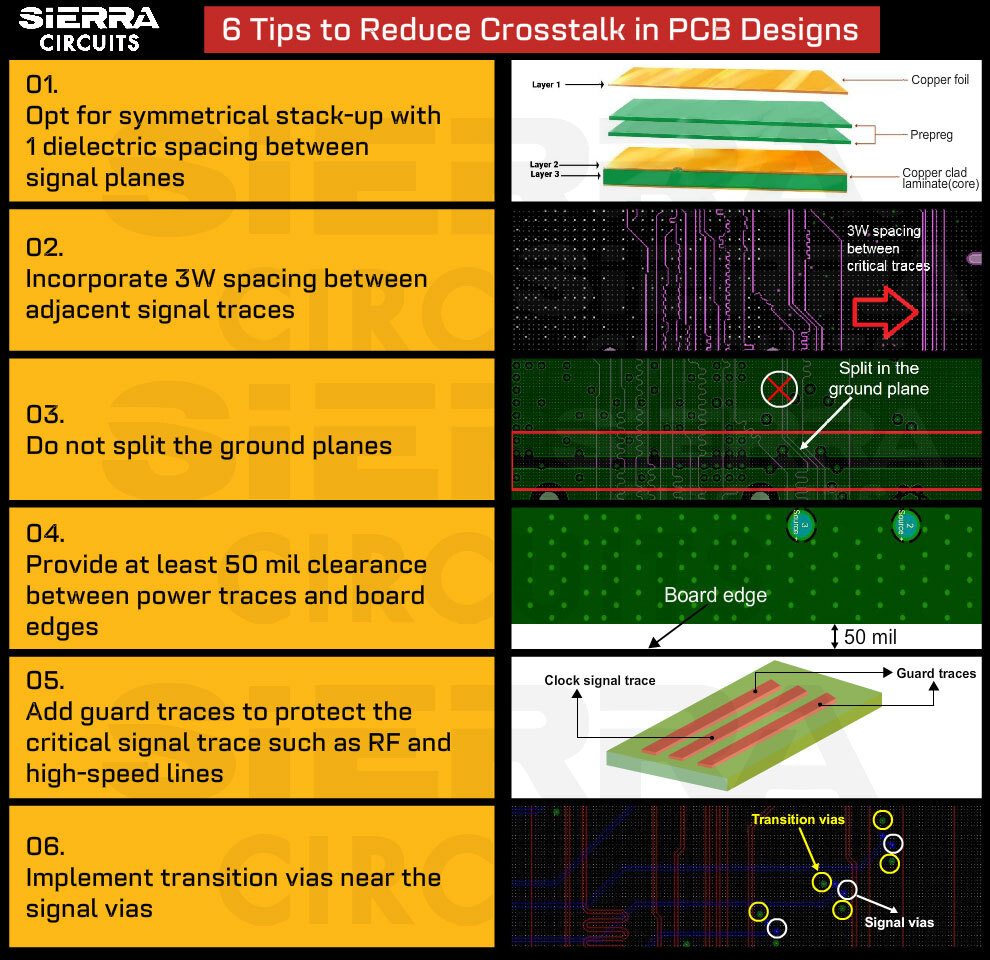

Handling Crosstalk in High-Speed PCB Design | Sierra Circuits – #55

Handling Crosstalk in High-Speed PCB Design | Sierra Circuits – #55

Posts: guard ring layout technique

Categories: Rings

Author: dienmayquynhon.com.vn